ISE仿真中需要注意的问题

2012-06-02

iamfrankie

13

在我们团队负责的项目光栅传感器系统高频并行解调算法的FPGA实现中,需要直接频率合成模块,因此我们想在FPGA上实现一个DDS芯片的功能,最近在BASYS板上调通了DDS模块,在功能仿真过程中我们发现在ISE环境下编写VHDL时对信号赋初值对仿真是十分必要的。 由于参数的要求模块中用到了一个三分频电路。程序如下: library ..

[查看全文]

FPGA的FIR抽取滤波器的设计

2012-06-02

佟力永

9

1、引言 抽取滤波器广泛应用在数字接收领域,是数字下变频器的核心部分。目前,抽取滤波器的实现方法有3种:单片通用数字滤波器集成电路、DSP和可编程逻辑器件。使用单片通用数字滤波器很方便,但字长和阶数的规格较少,不能完全满足实际需要。使用DSP虽然简单,但程序要顺序执行,执行速度必然慢。现场可编程门阵列(FPGA ..

[查看全文]

嵌入式处理器Nios II与液晶显示模块的接口及应用

2012-06-02

包明 余成波

10

液晶显示器(LCD)由于具有工作电压低、功耗低、体积小、显示信息量大、寿命长、不产生电磁辐射污染、可以显示复杂的文字及图形等优点,液晶显示器已被广泛应用于各种仪器仪表、电子设备及控制领域中,成为测量结果显示和人机对话的重要工具。液晶显示器按其功能可分为笔段式和点矩阵式液晶显示器,后者又可以分为字符点阵式 ..

[查看全文]

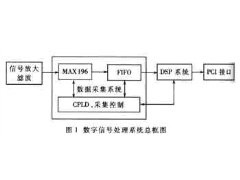

用Verilog HDL设计自动数据采集系统

2012-06-02

10

随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。从电子CAD、电子CAE到电子设计自动化(EDA ..

[查看全文]

FPGA四阶IIR数字滤波器实现

2012-06-02

10

常用的数字滤波器有FIR数字滤波器和IIR数字滤波器。FIR数字滤波器具有精确的线性相位特性,在信号处理方面应用极为广泛,而且可以采用事先设计调试好的FIR数字滤波器IPCore来完成设计,例如Altera公司提供的针对Altera系列可编程器件的MegaCore,但是需要向Altera公司购买或申请试用版。另外,对于相同的设计指 ..

[查看全文]

FPGA实现信号延时的方法

2012-06-02

16

FPGA实现信号延时的方法汇总: 1、门延时数量级的延时(几个ns),可用逻辑门来完成,但告诉综合器不要将其优化掉(不精确,误差大,常常不被推荐)。比如用两个非门(用constraint 来告诉synthesizer 不要综合掉这些逻辑)。 2、使用delay cell,lcell。 3、采用更快的时钟,通过计数器来实现,对于比较小的延时,用两个DFF 级联就 ..

[查看全文]

在Matlab中实现FPGA硬件设计

2012-06-02

江 霞

30

摘要 :System Generator for DSP是Xilinx公司开发的基于Matlab的DSP开发工具?熗?时也是一个基于FPGA的信号处理建模和设计工具。文章介绍了在Matlab中使用System Generator for DSP实现FPGA硬件设计的方法,同时给出了一个应用实例。 关键词 :Matlab;FPGA;System Generator;DSP 近年来,在数字通信、网络、视 ..

[查看全文]

ADC0809 VHDL控制程序

2012-06-02

39

--文件名:ADC0809.vhd --功能:基于VHDL语言,实现对ADC0809简单控制 --说明:ADC0809没有内部时钟,需外接10KHz~1290Hz的时钟信号,这里由FPGA的系 --统时钟(50MHz)经256分频得到clk1(195KHz)作为ADC0809转换工作时钟。 --最后修改日期:2004.3.20 library ieee; use ieee.std_logic_1164.all; use ieee.std ..

[查看全文]

ModelSim作布局布线后仿真的库问题

2012-06-02

12

Modelsim是目前最流行的应用最广泛的FPGA仿真器,是Mentor Graphics的子公司Model Technology开发的。因为Modelsim好学易用,调试方便,仿真速度快,功能强大,所以很多芯片厂商的开发系统都OEM Mentor Graphics公司的Modelsim仿真器,包括Xilinx,Altera,Lattice和Actel等。Modelsim是一个单内核仿真器,同一个内 ..

[查看全文]

基于FPGA的IIR数字滤波器的快捷设计

2012-06-02

童位理

16

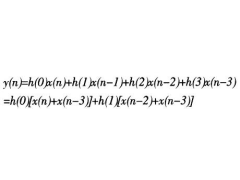

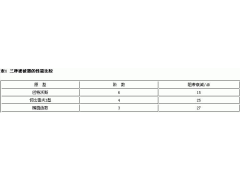

IIR数字滤波器在很多领域中都有着广阔的应用。与FIR数字滤波器相比,IIR数字滤波器可以用较低的阶数获得较高的选择性,而且所用存储单元少。经济效率高。一个N阶IIR数字滤波器的系统函数为: 其线性常系数差分方程为: 用FPGA实现滤波的基本思想就是基于式(2)来实现的。如果知道了系统的输入序列(滤波器的输入),那么,只要 ..

[查看全文]

Verilog HDL代码描述对状态机综合的研究

2012-06-02

李玲 王祖强 陈东海

5

1 引言 Verilog HDL作为当今国际主流的HDL语言,在芯片的前端设计中有着广泛的应用。它的语法丰富,成功地应用于设计的各个阶段:建模、仿真、验证和综合等。可综合是指综合工具能将Verilog HDL代码转换成标准的门级结构网表,因此代码的描述必须符合一定的规则。大部分数字系统都可以分为控制单元和数据单元两个部分,控制单元 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

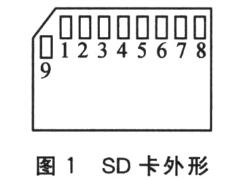

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300