从实例中学习OrCAD-PSpice 10.3-AA(第7章 电应力工具)

2012-06-02

21

第7章 电应力(Smoke)工具的使用 电子电路在工作过程中,常因某(些)个元器件承受的热电应力超出其安全工作条件,降低其可靠性,严重地导致冒烟烧毁。因此,“冒烟报警”提高电路工作的可靠性,对一些安全性要求较高的电路(网络)采用降额设计已纳入电子工程师视野。本章结合电路实例简介可靠性、降额设计的基 ..

[查看全文]

modelsim for linux安装指南

2012-06-02

18

for modelsim: 1 下载modelsim for linux的下载文件。应该总共有三个文件,分别是base,docs和linux.exe。都是gz压缩的。 2 解压缩linux.exe,解出来的是可以在终端中直接运行的文件,运行之,并安装。 3 分别解压base和docs在同一目录下。 4 把这时候的modeltech目录(也就是解压缩和安装后形成的目录)移动到你希望程序所存放 ..

[查看全文]

Verilog HDL代码描述对状态机综合的研究

2012-06-02

李玲 王祖强 陈东海

5

1 引言 Verilog HDL作为当今国际主流的HDL语言,在芯片的前端设计中有着广泛的应用。它的语法丰富,成功地应用于设计的各个阶段:建模、仿真、验证和综合等。可综合是指综合工具能将Verilog HDL代码转换成标准的门级结构网表,因此代码的描述必须符合一定的规则。大部分数字系统都可以分为控制单元和数据单元两个部分,控制单元 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 754

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 44

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

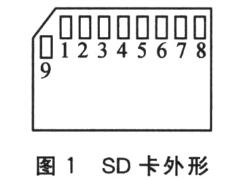

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 47

热门文章

-

C99语法规则2024年11月16日 754

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300