TEXTIO及其在VHDL仿真中的应用

2012-06-02

于红旗

12

TEXTIO 在VHDL 仿真与磁盘文件之间架起了桥梁,使用文本文件扩展VHDL 的仿真功能。本文介绍TEXTIO 程序包,以一个加法器实例说明TEXTIO 的使用方法,最后使用ModelSim 对设计进行仿真,并分析仿真结果。 在对VHDL 源程序进行仿真时, 由于有的输入输出关系仅仅靠输入波形或编写testbench 中的信号输入是难以验证结果正确 ..

[查看全文]

FPGA有限状态机模拟I2C总线设计

2012-06-02

潘小冬

15

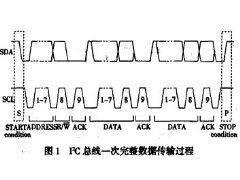

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模 ..

[查看全文]

利用有限状态机控制A/D采样

2012-06-02

13

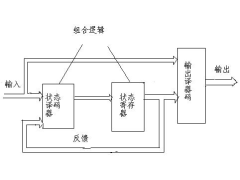

1 状态机的基本结构和功能 状态机是一类很重要的时序电路,是许多数字电路的核心部件。状态机的一般形式如图1所示。除了输入信号、输出信号外,状态机还包括一组寄存器,它用于记忆状态机的内部状态。状态机寄存器的下一个状态及输出,不仅同输入信号有关,而且还于寄存器当前状态有关。寄存器可以认为是组合逻辑和寄存器逻辑 ..

[查看全文]

怎样在NIOSII中操作PIO?

2012-06-02

GardenSu

11

运用NIOS II_IDE向导,在niosII_cyclone_1c20small下新建一个hello_led工程。 其中hello_led.c是这样写IO口的: IOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE, led); 首先在altera_avalon_pio_regs.h找到定义 代码 #include #define IORD_ALTERA_AVALON_PIO_DATA(base) IORD(base, 0) #define IOWR_ALTERA_AVALON ..

[查看全文]

使用基于FPGA的硬件方法实现算法加速

2012-06-02

Lara Simsic

11

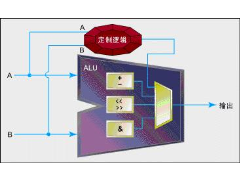

当设计者试图从算法中获得最佳性能但软件方法已无计可施时,可以尝试通过硬件/软件重新划分来进行加速。FPGA易于实现软件模块和硬件模块的相互交换,且不必改变处理器或进行板级变动。本文阐述如何用FPGA来实现算法的硬件加速。 如果想从代码中获得最佳性能,方法包括优化算法、使用查找表而不是算法、将一切都转换为本地 ..

[查看全文]

modelsim仿真问题

2012-06-02

84

近段时间比较忙,尝试着将工作中碰到的问题记录下来,也许它在某一天它会变成一笔财富了?不管怎么说,尝试记录工作的点滴都是一个不错的点子,呵呵。夸奖一下我自己! 在用modelsim 6.0 se作仿真的时候碰到一个错误,在xilinx的数据库里面发现原因如下: Problem Description: Keywords: ModelSim, MXE, MTI, error, VSIM ..

[查看全文]

ModelSim se完全编译Xilinx库文件

2012-06-02

16

什么是之前的老办法呢? Modlesim 仿真库的建立: 将Modelsim根目录下的modelsim.ini的属性由只读改为可写。 新建一个文件夹,比如library(为叙述方便,把它放在modelsim的根目录下)。D:/modelsim/library. 启动Modelsim,选择[File]/[chang Directory],选择D:/modelsim/library. 选择[File]/[New]/[library]命令,弹出[C ..

[查看全文]

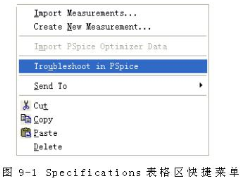

从实例中学习OrCAD-PSpice 10.3-AA(第9章 仿真的故障排除)

2012-06-02

41

第9章 仿真的故障排除 在运行高级分析工具的过程中,由于操作失误、参数设置不合理等方面的原因,常常出现错误信息或者系统仿真不能运行等情况,用户往往得不到理想的分析结果,面对这些存在的难题,不能坐着发闷,要积极的解决问题。本章主要介绍运用故障排除分析工具解决存在问题的使用方法及高级分析中一般性故障的解决方 ..

[查看全文]

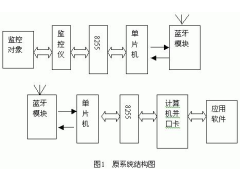

蓝牙HCI-UART与并口的FPGA控制接口设计

2012-06-02

10

摘要:某应用蓝牙技术的医疗监控系统中,单片机是其数据传输瓶颈。本设计采用FPGA取代了原系统的单片机和8255芯片,使数据传输速率提高了近10倍。文中讨论了设计的一些关键问题。 1 引言 在蓝牙体系的实现方案中, HCI意义重大,它以一个统一的接口实现主机设备与蓝牙模块之间的互操作。蓝牙HCI层定义了数据、命令、事件三类 ..

[查看全文]

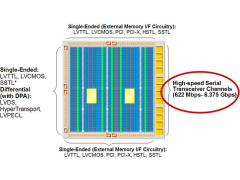

高速FPGA系统的信号完整性测试和分析

2012-06-02

张楷

41

1. 引言 随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。典型的高速FPGA器件提供的每一条物 ..

[查看全文]

Verilog Pli的基本使用方法(modelsim)

2012-06-02

15

内容未做证实,仅供参考。 1.hello.c文件内容 #include #include "veriuser.h" static PLI_INT32 hello() { printf("Hi there\n"); return 0; } s_tfcell veriusertfs[] = { {usertask, 0, 0, 0, hello, 0, "$hello"}, {0} /* last entry must be 0 */ }; 2.hello.v文件内容 module hello; initial begin $hello ..

[查看全文]

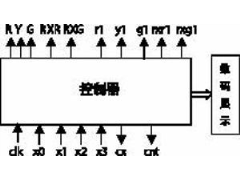

基于CPLD的交通灯控制系统

2012-06-02

孙芹芝 张瑾 苏晓鹭

17

引言 EDA技术是用于电子产品设计中比较先进的技术,可以代替设计者完成电子系统设计中的大部分工作,而且可以直接从程序中修改错误及系统功能而不需要硬件电路的支持,既缩短了研发周期,又大大节约了成本,受到了电子工程师的青睐。 实现路口交通灯系统的控制方法很多,可以用标准逻辑器件、可编程序控制器PLC、单片机等方案 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

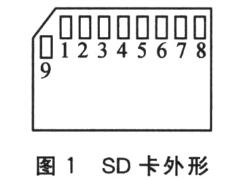

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300