Nios II开发环境中如何添加客户定制逻辑

2014-11-10

9

相比于MCS51,或者ARM,Nios II这种软核处理器的第一个特别有用的特性是可以方便得添加客户定制逻辑。这是一个非常有趣并且重要的特性。在这里,我粗略得介绍一下在Nios II开发环境中如何添加客户定制逻辑;更加详细的帮助信息请您参考Altera公司提供的文档。如果本文能对您有一点点帮助,我都会感到非常高兴。 1、准备工作 ..

[查看全文]

基于MATLAB在IIR滤波器的设计与仿真

2014-11-10

肖卫初 钟川桃

18

1 引言在现代通信系统中,由于信号中经常混有各种复杂成分,所以很多信号的处理和分析都是基于滤波器而进行的。但是,传统的数字滤波器的设计使用繁琐的公式计算,改变参数后需要重新计算,从而在设计滤波器尤其是高阶滤波器时工作量很大。利用MATLAB信号处理箱(Signal Processing Toolbox)可以快速有效地实现数字滤波器的 ..

[查看全文]

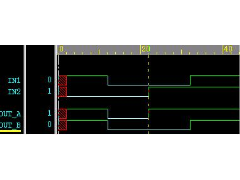

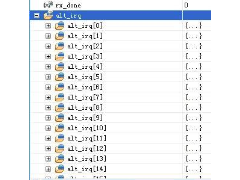

异步FIFO的VHDL设计

2013-04-06

9

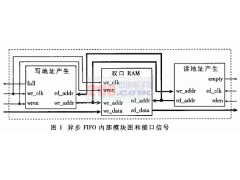

FIFO(先进先出队列)是一种在电子系统得到广泛应用的器件,通常用于数据的缓存和用于容纳异步信号的频率或相位的差异。FIFO的实现通常是利用双口RAM和读写地址产生模块来实现的。FIFO的接口信号包括异步的写时钟(wr_clk)和读时钟(rd_clk)、与写时钟同步的写有效(wren)和写数据(wr_data)、与读时钟同步的读有 ..

[查看全文]

在Modelsim se中创建altera仿真库

2013-04-06

20

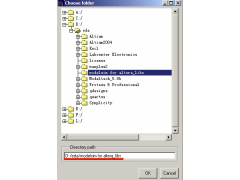

1. 路径选择 启动modelsim se仿真工具,在主窗口中选择【file】→【change directory】命令,将工作目录改变到你想存放仿真库的目录,点击【ok】. 2. 创建仿真库 在生窗口中选择【file】→【new】→【library】命令,在弹出的【create a new library】窗口中将选项【create】设置为【a new library and a logical ma ..

[查看全文]

Xilinx DCM的使用

2013-04-06

8

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构 ..

[查看全文]

VHDL 计数器源程序

2013-04-05

8

十五计数器library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; ENTITY fiveteencout IS PORT(clk,reset,enable : IN std_logic; count : OUT std_logic_vector(3 downto 0)); END fiveteencout; ARCHITECTURE counter OF fiveteencout IS SIGNAL count_int:std_logic_vector(0 to 3); BEGIN PROC ..

[查看全文]

如何保证RTL设计与综合后网表的一致性

2013-04-05

王振国

7

文章简介:在超大规模数字集成电路的设计中,我们使用逻辑综合工具来完成从RTL设计到门级网表的转化。我们希望它综合出的门级网表与我们的RTL设计在逻辑和时序上完全一致。但是某些书写风格和设计思路却会造成两者不一致的情况,降低我们的工作效率。本文列举了三种RTL设计与综合后网表不一致的情况,并给出了解决方法.我 ..

[查看全文]

在ModelSim波形图中以参数名显示变量

2013-04-04

13

在使用Verilog HDL编写有限状态机等逻辑的时候,状态机的各个状态通常以参数表示,但当使用ModelSim仿真的时候,状态机变量在wave窗口中以二进制编码的形式显示,例如:4’h0、4’h1等。这种显示形式不是很直观,但我们可以使用ModelSim提供的命令将状态机变量以“文本”形式的参数名显示,从而有 ..

[查看全文]

Nios II中断简述及中断调试技巧

2013-04-03

8

一、Nios II中断简述 Nios II 的中断处理方式带有典型的RISC处理器的特征,所有的中断处理都从同一入口进入,然后由软件加以分配。负责分配工作的软件叫系统ISR,它是由开发系统提供的,自动的连接到可执行程序上。系统ISR维护着一个中断向量表,表中的每一项代表着一个专项处理程序的入口。所有的专项处理程序都是由用户定义然 ..

[查看全文]

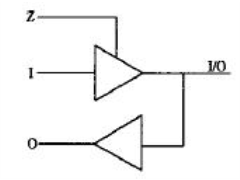

FPGA中双向端口I/O的研究

2013-04-03

莫海永 张申科

7

摘要针对现场可编程门阵列(FPGA)芯片的特点,研究 FPGA 中双向端口I/O 的设计,同时给出仿真初始化双向端口I/O 的方法。 采用这种双向端口的设计方法,选用 Xilinx 的Spartan2E 芯片 设计一个多通道图像信号处理系统。引言FPGA 是现场可编程门 阵 列 的 缩 写,它 是 在PAL,GAL 及 EPLD 等可编程器件的基础上发展起 来的。FPGA ..

[查看全文]

NIOS-II学习日记

2013-04-03

5

2006年12月07日:以下是我的NIOS-II调试经历,与大家分享: 在拿到FPGA时,很高兴,可以搞NIOS了(一阵激动,都忘了常规检查流程啦!)。拿到时,朋友说调试过的没有问题。我就拿起电路图(pdf),找到时钟输入脚(125,奇怪为什么这个脚是普通IO脚,没看到全局时钟脚呢, 管它的就按此脚使用吧)。 就搞了个计数器,把时钟5 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 754

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 44

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

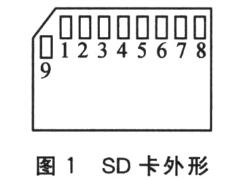

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 47

热门文章

-

C99语法规则2024年11月16日 754

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300