用VHDL设计乐曲发生器

2012-06-02

姜田华

13

1 概述随着EDA 技术的进展,基于可编程 ASIC 的数字电子系统设计的完整方案越来越受到人们的重视,并且以 EDA 技术为核心的能在可编程 ASIC 上进行系统芯片集成的新设计方法,也正在快速地取代基于 PCB板的传统设计方式。 与利用微处理器(CPU 或MCU)来实现乐曲演奏相比,以纯硬件完成乐曲演奏电路的逻辑要复杂得多,如果不 ..

[查看全文]

verilog HDL设计练习进阶(一)

2012-06-02

4

练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法。 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 模块源 ..

[查看全文]

一个简单的总线轮询仲裁器Verilog代码

2012-06-02

15

下面这个是以输入信号作为状态机的转移条件,写得比较冗余: // // Verilog Module demo1_lib.bus_arbitor.arch_name // // Created: //by - Newhand //in - Shanghai ZhangJiang //at - 20:39:41 2003-12-03 // using Mentor Graphics HDL Designer(TM) // ///////////////////////////////////////////////////////// ..

[查看全文]

Verilog-HDL仿真软件ModelSim的基本操作

2012-06-02

常晓明

10

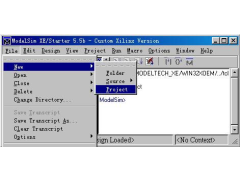

Verilog-HDL与CPLD/FPGA设计应用讲座 第 4 讲 Verilog-HDL仿真软件的基本操作 4.1 建立新的工程文件 4.2 一个最简单的仿真实例 在本讲以Xilinx WebPACK 4.1 ModelSim XE Starter为例,说明仿真软件的基本操作。 4.1 建立新的工程文件 启动Xilinx WebPACK 4.1 ModelSim XE Starter后,选中【File】菜单中的【New】菜单项, ..

[查看全文]

FPGA三国志-第一篇/不可不看的故事

2012-06-02

wisdomz

5

CPLD的时代 我在12年前,偶然接触PLD,没有想到自己居然就在这个行当里安身下来。可是这个行业也的确是个飞速发展的行业,十多年过去后,从当初的接近十家主要供应商,到今天已经激烈搏杀后,只有差不多如论坛题目一样的,成为了今天三足鼎立的局面。想来想去,决定以这个名字作为论坛的主题。同时也和大家分享我多年来的一 ..

[查看全文]

自制wiggler-附原理图

2012-06-02

31

关于JTAG的原理,大家可以参考OPEN-JTAG 开发小组写的《ARM JTAG 调试原理》。JTAG、BDM 都比较类似,实际上是将仿真功能嵌入到芯片内部,接上比较简单的调试工具就可以进行开发了,省掉了高价的仿真器。 JTAG 调试用到了 TCK、TMS、TDI、TDO 和 TRST这几个脚。其中 TRST 是用来对 TAP controller进行复位的,它 ..

[查看全文]

FPGA直接数字频率合成器的设计

2012-06-02

周俊峰 陈 涛

5

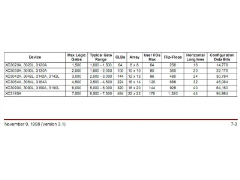

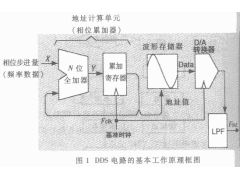

摘要:介绍了利用Altera的FPGA器件(ACEX EP1K50)实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。 关键词:直接数字频率合成(DDS) 现场可编程门阵列(FPGA) 直接数字频率合成(Direct Digital Fraquency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需要波形的一种新的频率 ..

[查看全文]

VHDL语言程序配置EAB的研究

2012-06-02

何永泰

20

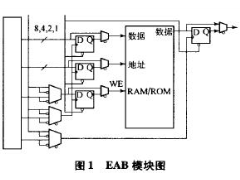

摘要: 在FPGA(现场可编程门阵列)的使用中,要将VHDL(甚高速集成电路硬件描述语言)编写的程序配置到EAB(嵌入式阵列块)单元中,会遇到许多问题,配置很难成功。根据配置EAB的经验,详细介绍了正确配置EAB的方法。 1、引言 FLEX10K器件是工业界第一个嵌入式的PLD(可编程逻辑器件),由于其具有高密度、低成本、低功率等特点,成 ..

[查看全文]

基于Nios软核CPU的uC/OS-II和LwIP移植

2012-06-02

李正军

15

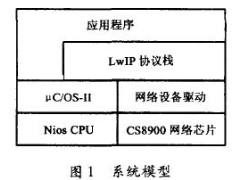

Altera公司推出的Nios软核CPU是一种可配置的通用精简指令集计算RISC(Reduced Instruction Set Computing)嵌入式处理器。它可以与各种外设相结合,构成一个定制的可编程片上系统SOPC(System on Programable Chip)。嵌入式实时操作系统uC/OS-II是一个非常优秀的实时操作系统RTOS(Real Time Operating System),其性能 ..

[查看全文]

ModelSim SE仿真Altera库的建立

2012-06-02

shemily

23

(注:最近自己准备做后仿真,到坛子里看看了,发现一开始建库就是一个很大的问题。为了便以自己学习也为了给大家省点事,我花了十来个小时整理了一些资料,全部资料来自edacn.net/bbs的ModelSim的〈库〉,在下面的资料中不能一一列出作者,请各位网友多多包涵。下面的资料是大家的成果。by CHY 07.04.05) 1. modelsim怎 ..

[查看全文]

基于VHDL语言的 IP 核验证

2012-06-02

13

摘要:探讨了IP核的验证与测试的方法及其和VHDL语言在IC设计中的应用.并给出了其在RISC8框架CPU核中的下载实例 引言 在IC(integrated circuit.集成电路)发展到超大规模阶段的今天,基于IP(Intellectual Property,知识产权)核的IC设计及其再利用是保证SoC(system onchip,片上系统)开发效率和质量的重要手段。如果能对IP ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

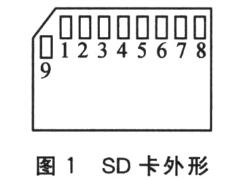

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300