练习一.简单的组合逻辑设计

目的: 掌握基本组合逻辑电路的实现方法。

这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

模块源代码:

//--------------- compare.v -----------------

module compare(equal,a,b);

input a,b;

output equal;

assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时,

//equal输出为0。

endmodule

测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。

测试模块源代码:

`timescale 1ns/1ns //定义时间单位。

`include "./compare.v" //包含模块文件。在有的仿真调试环境中并不需要此语句。

//而需要从调试环境的菜单中键入有关模块文件的路径和名称

module comparetest;

reg a,b;

wire equal;

initial //initial常用于仿真时信号的给出。

begin a=0;

b=0;

#100 a=0;

b=1;

#100 a=1;

b=1;

#100 a=1;

b=0;

#100 $stop; //系统任务,暂停仿真以便观察仿真波形。

end

compare compare1(.equal(equal),.a(a),.b(b)); //调用模块。

endmodule

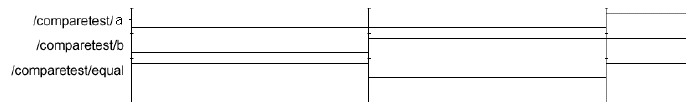

仿真波形(部分):

练习: 设计一个字节(8位)比较器。

要求:比较两个字节的大小,如a[7:0]大于 b[7:0]输出高电平,否则输出低电平,改写测试模型,使其能进行比较全面的测试 。

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 192

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261