基于FPGA的多路脉冲重复频率跟踪器

2012-06-02

12

摘要:在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟踪器,它解决了在密集信号环境下信号跟踪的实时性问题,减小了系统体积。经过实验验证,其各项指标均达到了设计要求。 随着高科技的迅速发展,现代战争已经不仅是传统意义战场上 ..

[查看全文]

基于VHDL语言的 IP 核验证

2012-06-02

13

摘要:探讨了IP核的验证与测试的方法及其和VHDL语言在IC设计中的应用.并给出了其在RISC8框架CPU核中的下载实例 引言 在IC(integrated circuit.集成电路)发展到超大规模阶段的今天,基于IP(Intellectual Property,知识产权)核的IC设计及其再利用是保证SoC(system onchip,片上系统)开发效率和质量的重要手段。如果能对IP ..

[查看全文]

verilog HDL设计练习进阶(一)

2012-06-02

4

练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法。 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 模块源 ..

[查看全文]

Verilog脉冲发生器程序

2012-06-02

万雪松

24

/*************************************************************************************** 实现功能简述 本模块主要功能是产生一个确定时钟周期长度(最长为256个时钟周期)的脉冲信号,可以自己设定脉冲长度,输出的脉冲信号与时钟上升沿同步 脉冲宽度 = pulsewide + 1 时钟周期; 输入一个启动信号后,可以产生一个 ..

[查看全文]

蓝牙HCI-UART与并口的FPGA控制接口设计

2012-06-02

10

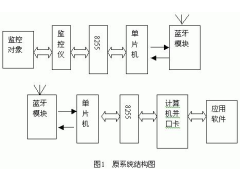

摘要:某应用蓝牙技术的医疗监控系统中,单片机是其数据传输瓶颈。本设计采用FPGA取代了原系统的单片机和8255芯片,使数据传输速率提高了近10倍。文中讨论了设计的一些关键问题。 1 引言 在蓝牙体系的实现方案中, HCI意义重大,它以一个统一的接口实现主机设备与蓝牙模块之间的互操作。蓝牙HCI层定义了数据、命令、事件三类 ..

[查看全文]

静态时序分析在高速FPGA设计中的应用

2012-06-02

周海斌

27

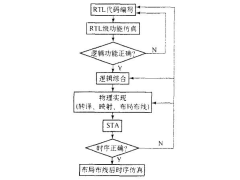

摘要:介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进时序收敛的方法。结合设计实例,阐明了STA在高速、大规模FPGA开发中的应用。实践表明,随着数字设计复杂度的增加,在后端的时序验证环节,与传统的动 ..

[查看全文]

Nios II在电机伺服控制中的应用

2012-06-02

8

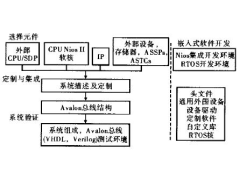

1 引言 Nios II系列32位RISC嵌入式处理器是Altera公司的第二代软核嵌入式处理器,性能超过200DMIPS Nios II处理器是软核,开发者能够从无限的系统配置组合中选择满足性能和成本目标的方案,而不必为系统级设计采用ASIC,这种开发方式非常适合设计针对网络、电信、数据通信、嵌入式和消费市场的各种嵌入式应用。本文采用Nios ..

[查看全文]

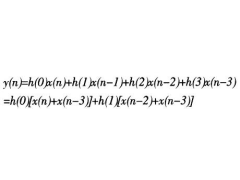

FPGA的FIR抽取滤波器的设计

2012-06-02

佟力永

9

1、引言 抽取滤波器广泛应用在数字接收领域,是数字下变频器的核心部分。目前,抽取滤波器的实现方法有3种:单片通用数字滤波器集成电路、DSP和可编程逻辑器件。使用单片通用数字滤波器很方便,但字长和阶数的规格较少,不能完全满足实际需要。使用DSP虽然简单,但程序要顺序执行,执行速度必然慢。现场可编程门阵列(FPGA ..

[查看全文]

ModelSim SE仿真Altera库的建立

2012-06-02

shemily

23

(注:最近自己准备做后仿真,到坛子里看看了,发现一开始建库就是一个很大的问题。为了便以自己学习也为了给大家省点事,我花了十来个小时整理了一些资料,全部资料来自edacn.net/bbs的ModelSim的〈库〉,在下面的资料中不能一一列出作者,请各位网友多多包涵。下面的资料是大家的成果。by CHY 07.04.05) 1. modelsim怎 ..

[查看全文]

自制wiggler-附原理图

2012-06-02

32

关于JTAG的原理,大家可以参考OPEN-JTAG 开发小组写的《ARM JTAG 调试原理》。JTAG、BDM 都比较类似,实际上是将仿真功能嵌入到芯片内部,接上比较简单的调试工具就可以进行开发了,省掉了高价的仿真器。 JTAG 调试用到了 TCK、TMS、TDI、TDO 和 TRST这几个脚。其中 TRST 是用来对 TAP controller进行复位的,它 ..

[查看全文]

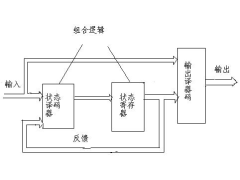

利用有限状态机控制A/D采样

2012-06-02

13

1 状态机的基本结构和功能 状态机是一类很重要的时序电路,是许多数字电路的核心部件。状态机的一般形式如图1所示。除了输入信号、输出信号外,状态机还包括一组寄存器,它用于记忆状态机的内部状态。状态机寄存器的下一个状态及输出,不仅同输入信号有关,而且还于寄存器当前状态有关。寄存器可以认为是组合逻辑和寄存器逻辑 ..

[查看全文]

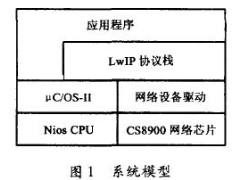

基于Nios软核CPU的uC/OS-II和LwIP移植

2012-06-02

李正军

15

Altera公司推出的Nios软核CPU是一种可配置的通用精简指令集计算RISC(Reduced Instruction Set Computing)嵌入式处理器。它可以与各种外设相结合,构成一个定制的可编程片上系统SOPC(System on Programable Chip)。嵌入式实时操作系统uC/OS-II是一个非常优秀的实时操作系统RTOS(Real Time Operating System),其性能 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

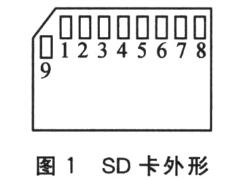

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300