debussy和modelsim协同仿真(VHDL)

2012-06-02

18

1、 编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。 2、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中 3、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录 4、 ..

[查看全文]

如何搭建Xilinx FPGA开发环境

2012-06-02

风子心

5

一、计算机硬件环境要求 : 1、操作系统: Microsoft Windows XP Home Edition SP2 2、基本配置: A、处理器:Intel CPU T2050 1.6GHz B、内存:512MB C、硬盘:60GB(其中软件安装的空问需要3GB) 补充: 上面的配置为笔记本的配置。因此对显卡没有什么特殊的要求。有条件的话,尽可能选择更高的配置。这样软件跑起来会更快。 ..

[查看全文]

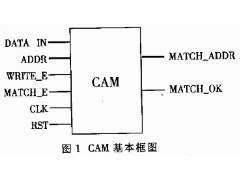

一种基于移位寄存器的CAM的Verilog HDL实现

2012-06-02

8

CAM(Content Addressable Memory,内容可寻址存储器)是一种特殊的存储阵列。它通过将输入数据与CAM中存储的所有数据项同时进行比较,迅速判断出输入数据是否与CAM中的存储数据项相匹配,并给出匹配数据项的对应地址和匹配信息。CAM以其高速查找、大容量等特点而被广泛地应用于电讯、网络等领域。 本文介绍一种用Ve ..

[查看全文]

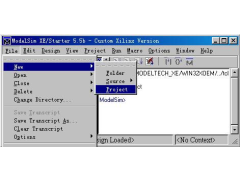

Verilog-HDL仿真软件ModelSim的基本操作

2012-06-02

常晓明

10

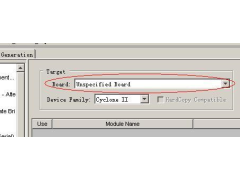

Verilog-HDL与CPLD/FPGA设计应用讲座 第 4 讲 Verilog-HDL仿真软件的基本操作 4.1 建立新的工程文件 4.2 一个最简单的仿真实例 在本讲以Xilinx WebPACK 4.1 ModelSim XE Starter为例,说明仿真软件的基本操作。 4.1 建立新的工程文件 启动Xilinx WebPACK 4.1 ModelSim XE Starter后,选中【File】菜单中的【New】菜单项, ..

[查看全文]

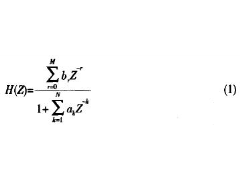

基于FPGA的IIR数字滤波器的快捷设计

2012-06-02

童位理

16

IIR数字滤波器在很多领域中都有着广阔的应用。与FIR数字滤波器相比,IIR数字滤波器可以用较低的阶数获得较高的选择性,而且所用存储单元少。经济效率高。一个N阶IIR数字滤波器的系统函数为: 其线性常系数差分方程为: 用FPGA实现滤波的基本思想就是基于式(2)来实现的。如果知道了系统的输入序列(滤波器的输入),那么,只要 ..

[查看全文]

Verilog HDL设计练习进阶(二)

2012-06-02

8

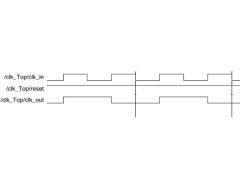

练习二. 简单时序逻辑电路的设计 目的:掌握基本时序逻辑电路的实现。 在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型,我们通常使用always块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个1/2分频器的可综合模型。 // half_clk.v: module half_clk( ..

[查看全文]

SystemVerilog语言简介

2012-06-02

39

SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、 接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。SystemVerilog由Accellera开发,它主要定位在芯片的 ..

[查看全文]

Nios II程序下载到Flash的方法

2012-06-02

lotol

7

我们在调试完Nios II系统后,接下来的工作就是要把程序固化到NOR Flash(以下简称Flash)中,让其上电后自动运行。但是这又该如何做呢?我想大家一定会想到使用Nios的Flash Programmer。没错,就是用它。不过,Flash Programmer也不是随便拿来就能用的,如果设置不正确,照样无法使用。闲话少说,follow me。 说明:设置 ..

[查看全文]

FPGA三国志-第一篇/不可不看的故事

2012-06-02

wisdomz

5

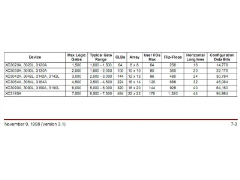

CPLD的时代 我在12年前,偶然接触PLD,没有想到自己居然就在这个行当里安身下来。可是这个行业也的确是个飞速发展的行业,十多年过去后,从当初的接近十家主要供应商,到今天已经激烈搏杀后,只有差不多如论坛题目一样的,成为了今天三足鼎立的局面。想来想去,决定以这个名字作为论坛的主题。同时也和大家分享我多年来的一 ..

[查看全文]

固定几何结构的FFT算法及其FPGA实现

2012-06-02

9

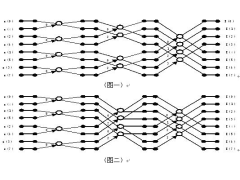

1.引言 DFT及其快速算法FFT是信号处理领域的核心组成部分。FFT算法多种多样,按数据组合方式不同一般分时域和频域,按数据抽取方式的不同又可分为基2,基4等。各算法的优缺点视不同的制约因素而不同。FFT的实现方法也多种多样,可以用软件实现,也可以用硬件实现,用软件在PC机或工作站上实现则计算速度很慢。一般多结合 ..

[查看全文]

一个简单的总线轮询仲裁器Verilog代码

2012-06-02

15

下面这个是以输入信号作为状态机的转移条件,写得比较冗余: // // Verilog Module demo1_lib.bus_arbitor.arch_name // // Created: //by - Newhand //in - Shanghai ZhangJiang //at - 20:39:41 2003-12-03 // using Mentor Graphics HDL Designer(TM) // ///////////////////////////////////////////////////////// ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

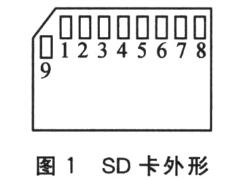

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300