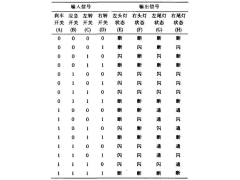

汽车车灯控制系统的VHDL语言实现

2012-06-02

郑应民

7

当前数字电路系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。利用大规模可编程逻辑器件CPLD(Complex Programmable Logic Device)进行ASIC设计,可以直接面向用户需求,根据对系统的功能要求自上而下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成元器件。目前,系统级的仿真工具也已出现.这样可以大 ..

[查看全文]

Altera FPGA、CPLD 学习笔记

2012-06-02

9

1.硬件设计基本原则 速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用 & ..

[查看全文]

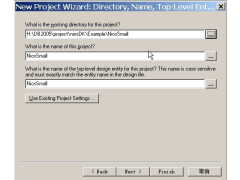

NiosII 快速入门(EDA软件的安装)

2012-06-02

6

Nios II是一个用户可配置的通用RISC嵌入式处理器。在这儿,我引用了Altera公司关于NiosII的官方介绍: Altera推出的Nios II系列嵌入式处理器扩展了目前世界上最流行的软核嵌入式处理器的性能,把Nios II嵌入到Altera的所有FPGA中,例如StratixII、Stratix、CycloneII,Cyclone、APEX,ACEX和HardCopy系列器件中,用户可以获 ..

[查看全文]

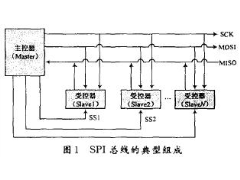

SPI串行总线接口的Verilog实现

2012-06-02

孙丰军 余春暄

15

摘 要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。重点描述了SPI串行总线接口在一款 ..

[查看全文]

fir滤波器的Verilog程序

2012-06-02

31

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date:17:01:38 10/09/06 // Design Name: // Module Name:ppeifir // Project Name: // Target Device: // Tool versions: // Description:用Verilog编写的fir滤波器程 ..

[查看全文]

Verilog交通灯控制器程序

2012-06-02

5

交通灯控制器 /* 信号定义与说明: CLK: 为同步时钟; EN: 使能信号,为1 的话,则控制器开始工作; LAMPA: 控制A 方向四盏灯的亮灭;其中,LAMPA0~LAMPA3,分别控制A 方向的 左拐灯、绿灯、黄灯和红灯; LAMPB: 控制B 方向四盏灯的亮灭;其中,LAMPB0 ~ LAMPB3,分别控制B 方向的 左拐灯、绿灯、黄灯和红灯; ACOU ..

[查看全文]

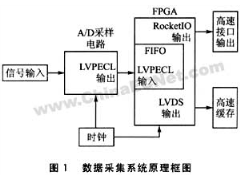

基于FPGA的高速数据采集系统接口设计

2012-06-02

黄伟,罗新民

14

当前,越来越多的通信系统工作在很宽的频带上,对于保密和抗干扰有很高要求的某些无线通信更是如此,随着信号处理器件的处理速度越来越快,数据采样的速率也变得越来越高,在某些电子信息领域,要求处理的频带要尽可能的宽、动态范围要尽可能的大,以便得到更宽的频率搜索范围,获取更多的信息量。因此,通信系统对信号处理 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第6章 蒙特卡洛工具)

2012-06-02

32

第6章 蒙特卡洛(Monte Carlo)工具的使用 PSpice一直重视所设计的电路,要能适合于批量生产的需要。现在PSpice10.3单独设立Monte Carlo工具,使这一项工作得到加强。本章先简介容差分析的基本概念,其后重点介绍Monte Carlo工具的使用方法。 6.1容差分析 前几章所述电路分析法时,已经提过只将元件视作理想元件按标称值进 ..

[查看全文]

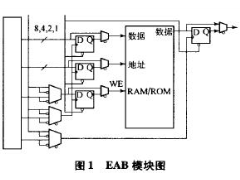

VHDL语言程序配置EAB的研究

2012-06-02

何永泰

20

摘要: 在FPGA(现场可编程门阵列)的使用中,要将VHDL(甚高速集成电路硬件描述语言)编写的程序配置到EAB(嵌入式阵列块)单元中,会遇到许多问题,配置很难成功。根据配置EAB的经验,详细介绍了正确配置EAB的方法。 1、引言 FLEX10K器件是工业界第一个嵌入式的PLD(可编程逻辑器件),由于其具有高密度、低成本、低功率等特点,成 ..

[查看全文]

FPGA四阶IIR数字滤波器实现

2012-06-02

10

常用的数字滤波器有FIR数字滤波器和IIR数字滤波器。FIR数字滤波器具有精确的线性相位特性,在信号处理方面应用极为广泛,而且可以采用事先设计调试好的FIR数字滤波器IPCore来完成设计,例如Altera公司提供的针对Altera系列可编程器件的MegaCore,但是需要向Altera公司购买或申请试用版。另外,对于相同的设计指 ..

[查看全文]

针对C语言编程者的Verilog开发指南

2012-06-02

13

本文举例说明了如何用软件实现脉宽调制(PWM),如何将该设计转换成一个可以在FPGA中运行的逻辑块,并能利用存储器映射I/O接口通过软件完成对该逻辑块的控制。通过理解本文讨论的概念和内容,没有太多硬件知识的软件开发人员也能掌握在FPGA上开发硬件的技能。 在不远的将来,嵌入式系统设计师将能够根据哪个更有利于解决设 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

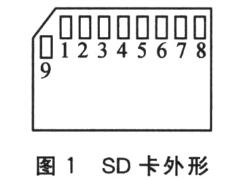

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300