基于VHDL 的全数字锁相环的设计

2012-12-29

倪虹霞 杨信昌

13

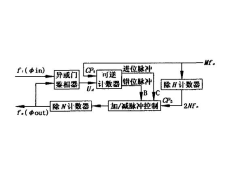

摘要:叙述了全数字锁相环的工作原理,提出了应用VHDL 技术设计全数字锁相环的方法,并用复杂可编程逻辑器件CPLD 予以实现,给出了系统主要模块的设计过程和仿真结果。 0引言 全数字锁相环(DPLL) 由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点。从而具备可靠性高、工作稳定、调节方便等优点。在调制解调、频率合 ..

[查看全文]

构筑Verilog-HDL设计所需要的环境

2012-12-27

常晓明

11

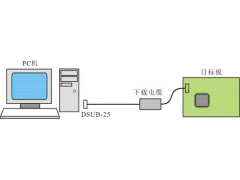

Verilog-HDL与CPLD/FPGA设计应用讲座 第 2 讲 构筑Verilog-HDL设计所需要的环境 2.1 进行Verilog-HDL设计需要什么样的环境? 2.2 软件的获取与安装 2.3 下载电缆与目标板 2.4 目标板 2.5 结语 2.1 进行Verilog-HDL设计需要什么样的环境? 2.1.1 硬件环境 要进行Verilog-HDL设计,首要的环境就是硬件环境。图1给出了进行Verilog ..

[查看全文]

Verilog 非阻塞赋值的仿真/综合问题

2012-12-27

16

源文件作者:Clifford E. Cummings(Sunburst Design, Inc.)原标题:Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill! ATTN:所有括号内“外注”为理解方便或有疑问的地方,原文里并没有。所有翻译都是为遵循“共同进步”的理想但并没有去努力得到原作者的任何书面和其它方式 ..

[查看全文]

VHDL实现多路彩灯控制器

2012-12-25

10

本文介绍应用美国ALTERA公司的MAX+Plus II平台,使用VHDL硬件描述语言实现的多路彩灯控制器。 一、多路彩灯控制器设计原理 设计一个彩灯控制程序器。可以实现四种花型循环变化,有复位开关。整个系统共有三个输入信号CLK,RST,SelMode,八个输出信号控制八个彩灯。时钟信号CLK脉冲由系统的晶振产生。各种不同花样彩灯 ..

[查看全文]

FPGA/CPLD状态机的稳定性研究

2012-12-25

宋烈武 石强

14

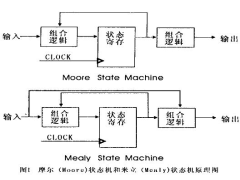

摘要 在FPGA/CPLD设计中频繁使用的状态机,常出现一些稳定性问题,本文提出了一些解决方法,实验表明该方法有效地提高了综合效率. 随着大规模和超大规模FPGA/CPLD器件的诞生和发展,以HDL(硬件描述语言)为工具、FPGA/CPLD器件为载体的EDA技术的应用越来越广泛.从小型电子系统到大规模SOC(Systemonachip)设计,已经无 ..

[查看全文]

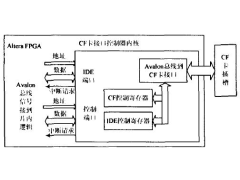

Nios II与CF卡的接口设计

2012-12-24

龚捷

11

1 CF卡的特点及应用 CF卡是最近几年蓬勃发展固态非易失的存储介质,由于CF卡具有携带方便、易于升级、存储量大、抗震性好等优点,在大容量便携式数据存储和传输过程中,CF 有着非常广泛的应用前景,如数码相机、MP3播放器、PDA(个人数字助理)、数字式录音机、笔记本电脑、手提电话、机顶盒等。预计今后在其他领域将有更为 ..

[查看全文]

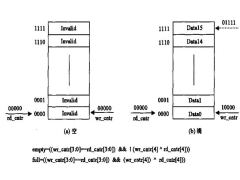

基于Verilog HDL语言的32X8 FIFO设计

2012-12-24

夏传红 王祖强 李秀娟

10

摘要:介绍了FIFO的基本概念、设计方法和步骤,采用了一种新颖的读、写地址寄存器和双体存储器的交替读、写机制,实现了FIFO的基本功能,同时使本32X8 FIFO拥有可同时读、写的能力,完全基于Verilog HDL语言实现了电路功能并应用Synopsys公司的DesignCompiler和VCS对其进行综合、仿真。 对基于单体存储器的FIFO,作为一种数据 ..

[查看全文]

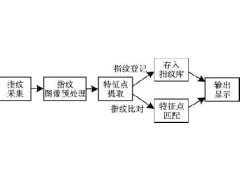

基于Nios II的自动指纹识别系统设计

2012-12-24

李莹 艾明晶

10

摘要 :介绍基于Nios II处理器的嵌入式自动指纹识别系统的实现方法;具体说明自动指纹识别系统的基本原理、系统总体结构、硬件结构设计、用户自定义指令的设计,以及指纹识别算法的处理流程和实现方法。 关键词 :嵌入式 指纹识别 Nios II 定制指令 引言 指纹识别作为生物特征识别的一种,在身份识别上有着其他手段不可比拟的优越性: ..

[查看全文]

利用FPGA实现PCI接口技术研究

2012-12-23

李廷军

16

摘要:介绍了状态机与PCI总线接口控制器的设计方法,探讨了如何利用VHDL语言在可编程器件FPGA 中实现基本传输控制的PCI总线控制器。测试结果表明设计符合PCI规范的时序要求。 PCI总线是目前应用最广泛的总线,它满足了用户对数据传输速率越来越高的要求。PCI局部总线是微型计算机中处理器/存储器与外围控制部件、扩展卡之间 ..

[查看全文]

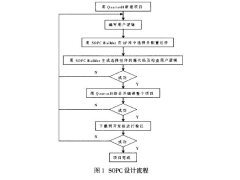

Nios II的USB接口模块设计

2012-12-23

郭文彬 孙智权

20

1.引言随着电路规模越来越大,片上系统(SoC)已经成为IC设计的发展趋势,相应地也有了更加灵活的片上可编程系统(SOPC)。Nios II CPU是一个基于流水线设计的通用RISC微处理器,拥有五级流水线和指令与数据内存分开的哈佛结构,具有可配置功能。用户可以根据需求在SOPC Builder中增减IP核,从而实现资源优化。为了构建一 ..

[查看全文]

VHDL设计举例:一个简单的UART

2012-12-22

16

---------------------------------------------------------------- -- -- Copyright (c) 1992,1993,1994, Exemplar Logic Inc. All rights reserved. -- ---------------------------------------------------------------- -- -- This design implements a UART. -- -- --Version 1.1 : Original Creation --Versi ..

[查看全文]

FFT的FPGA实现

2012-12-22

管吉兴

17

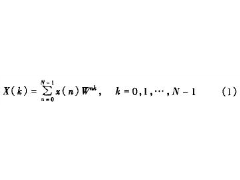

摘要:结合工程实践,介绍了一种利用FFT IP Core实现FFT的方法,设计能同时对两路实数序列进行256点FFT运算,并对转换结果进行求模平方运算,且对数据具有连续处理的能力。设计采用低成本的FPGA实现,具有成本低、性能高、灵活性强、速度快等特点,而且通过工程应用证明了设计是正确可行的。 由于FFT(快速傅里叶变换)的问 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 754

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 44

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

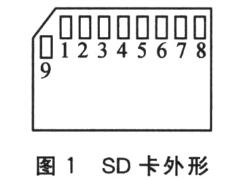

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 47

热门文章

-

C99语法规则2024年11月16日 754

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300