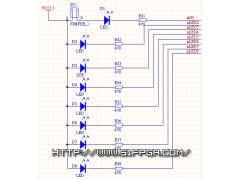

FPGA/CPLD实验教程一(点亮LED)

2013-01-19

抽烟的鱼

46

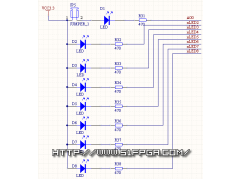

1. 实验要求及目的: 点亮发光二极管。通过这个实验,熟悉CPLD/FPGA开发软件的使用方法和开发流程及Verilog HDL 的编程方法。通过这个实验可以实际使用一下Quartus II软件,一通百通,下次就不讲那么详细了:) 使用软件:Quartus II 5.0。 2. 硬件原理图: 这个是我自己制作的开发板上的LED的原理图,一共有8个,IO和别的共 ..

[查看全文]

影响FPGA设计中时钟因素的探讨

2013-01-19

26

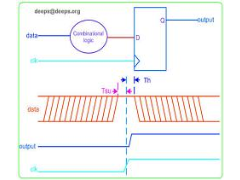

时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错;因而明确FPGA设计中决定系统时钟的因素,尽量较小时钟的延时对保证设计的稳定性有非常重要的意义。 1.1 建立时间与保持时间 建立时间(Tsu:set up time)是指在时钟 ..

[查看全文]

Verilog HDL常见问题

2013-01-19

4

问题:在使用case语句建模组合逻辑的时候,综合工具提示会出现latch 原因:产生这个错误时候可以从下面三个方面检查: 1. 看看这个语句块的敏感列表是否完备,也就是是否所有的“输入”信号都位于敏感列表内; 2. case语句是否覆盖了所有可能的条件; 3. “输出”信号是否在每个分支上都进行了赋值操作; 例 ..

[查看全文]

在Nios II中使用MicroCOS-II实时操作系统指南

2013-01-17

12

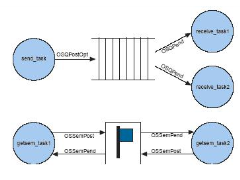

说明:该指南将会使你熟悉nios II IDE和MicroC/OS-II开发流程。niosII IDE提供设计者一个充足的niosII开发平台。niosII IDE包含MicroC/OS-II实时操作系统,为设计者提供快速地搭建基于niosII处理器的MicroC/OS-II应用程序的能力。该指南提供了搭建一个基于MicroC/OS-II实时操作系统的简单程序的步骤说明。 基于niosII处理器的M ..

[查看全文]

Nios II嵌入式Web服务器的实现

2013-01-16

赵不贿 孙智权 徐雷钧 郭文

9

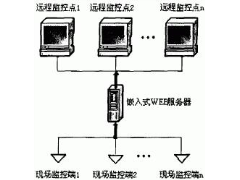

引 言 嵌入式系统是指被嵌入到各种产品或工程应用中以微处理器或微控制器为核心的软硬件系统。嵌入式系统与Internet技术相结合,形成的嵌入式 Internet技术是近几年随着计算机网络技术的普及而发展起来的一项新兴技术。工程技术人员、管理人员或调试人员通过Web而不用亲临现场就可以得到远程数据,并对测控仪器进行控制、校准 ..

[查看全文]

用FPGA实现实时视频处理

2013-01-15

13

随着数字融合的进一步发展,系统的设计和实现需要更大的灵活性,以解决将完全不同的标准和要求集成为同类产品时引发的诸多问题。本文介绍 FPGA在视频处理中的应用,与ASSP和芯片组解决方案相比,FPGA可根据当前(中国)设计工程师的实际需求提供不同层次的灵活性,并保持明显优于传统DSP的性能。 实时视频处理对系统性能的 ..

[查看全文]

Verilog电话计费器的代码

2013-01-15

11

/*信号定义: clk:时钟信号,本例中其频率值为1Hz; decide:电话局反馈回来的信号,代表话务种类,“01”表示市话,“10”表示 长话,“11”表示特话; dispmoney: 用来显示卡内余额,其单位为角,这里假定能显示的最大数额为50元(500角); disptime:显示本次通话的时长; write,r ..

[查看全文]

Cyclone II的DDR SDRAM接口实现

2013-01-14

24

在不增加电路板复杂度的情况下要想增强系统性能,改善数据位宽是一个有效的手段。通常来说,可以把系统频率扩大一倍或者把数据I/O管脚增加一倍来实现双倍的数据位宽。这两种方法都是我们不希望用到的,因为它们会增加整个设计系统的复杂度。在总的数据I/O管脚不变的情况下,使用双数据率(DDR)I/O管脚来传输和接收数据也能 ..

[查看全文]

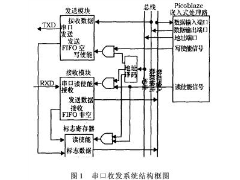

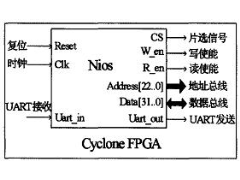

基于FPGA的SOC系统中的串口设计

2013-01-14

葛锐 欧钢

12

1 概述 在基于FPGA的SOC设计中,常使用串口作为通信接口,但直接用FPGA进行串口通信数据的处理是比较繁杂的,特别是直接使用FPGA进行串口通信的协议的解释和数据打包等处理,将会消耗大量的FPGA硬件资源。为简化设计,降低硬件资源开销,可以在FPGA中利用IP核实现的嵌入式微处理器来对串口数据进行处理。 本文中的设计采用了 ..

[查看全文]

FPGA/CPLD实验教程二(闪烁灯)

2013-01-13

抽烟的鱼

17

1. 实验要求及目的: 接着上次的实验,但是这次需要使8个LED周期性的闪烁。这次我就不详细的贴图说明每个步骤了,如果和上一个实验有不同的,需要特别说明的,我才贴图。 使用软件:Quartus II 5.0。 2. 硬件原理图: 这个是我自己制作的开发板上的LED的原理图,一共有8个,IO和别的共用的,使用八个LED的时候板上的JP1和JP ..

[查看全文]

FPGA字符型LCD模块控制

2013-01-13

12

字符型LCD模块价格便宜且便于和单片机或者FPGA连接。下面是一个1X16的字符型LCD模块。 为了控制LCD模块,一共需要11个引脚,其中包括8根数据线和3跟控制信号。这3个控制信号分别为: E:使能信号或者说是LCD片选信号,高有效 R/W:读/写信号,0:写,1:读 RS:寄存器选择,0:选择命令寄存器,1:选择数据寄存器 大多数的 ..

[查看全文]

基于Nios嵌入式软核处理器的液晶显示屏控制

2013-01-12

占荣 康勇

12

摘要 :Altera公司的 Nios嵌入式软核处理器以其成本低廉,设计灵活等特点,在嵌入式应用领域得到了广泛的应用,同时 LCD也越来越多地在各种仪器仪表和测控系统中作为人机界面和显示模块。本文提出一种基于Nios嵌入式软核处理器的液晶显示屏的软 、硬件设计方案,介绍了对该液晶屏进行控制的硬件接口电路以及软件编写流程,并给 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 754

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 44

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

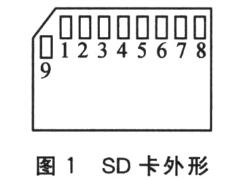

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 47

热门文章

-

C99语法规则2024年11月16日 754

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300