静态时序分析在高速FPGA设计中的应用

2012-06-02

周海斌

28

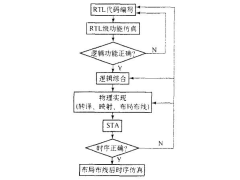

摘要:介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进时序收敛的方法。结合设计实例,阐明了STA在高速、大规模FPGA开发中的应用。实践表明,随着数字设计复杂度的增加,在后端的时序验证环节,与传统的动 ..

[查看全文]

基于FPGA的高速数据采集系统接口设计

2012-06-02

黄伟,罗新民

16

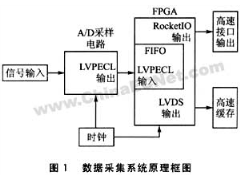

当前,越来越多的通信系统工作在很宽的频带上,对于保密和抗干扰有很高要求的某些无线通信更是如此,随着信号处理器件的处理速度越来越快,数据采样的速率也变得越来越高,在某些电子信息领域,要求处理的频带要尽可能的宽、动态范围要尽可能的大,以便得到更宽的频率搜索范围,获取更多的信息量。因此,通信系统对信号处理 ..

[查看全文]

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)

2012-06-02

常晓明 李媛媛

37

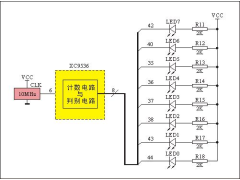

Verilog-HDL与CPLD/FPGA设计应用讲座 第 8 讲 用Verilog-HDL做CPLD设计 时序逻辑电路的实现 8.1 闪烁灯的实现 8.2 流水灯的实现 8.3 可编程单脉冲发生器 在第七讲中,已经介绍了组合逻辑电路的实现。组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。时序逻辑电路则不同于它,其特点是:在任意 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

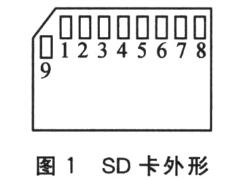

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317