Verilog HDL设计练习进阶(二)

2012-06-02

12

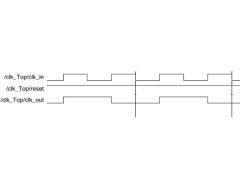

练习二. 简单时序逻辑电路的设计 目的:掌握基本时序逻辑电路的实现。 在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型,我们通常使用always块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个1/2分频器的可综合模型。 // half_clk.v: module half_clk( ..

[查看全文]

SystemVerilog语言简介

2012-06-02

44

SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、 接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。SystemVerilog由Accellera开发,它主要定位在芯片的 ..

[查看全文]

一种基于移位寄存器的CAM的Verilog HDL实现

2012-06-02

12

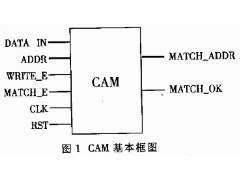

CAM(Content Addressable Memory,内容可寻址存储器)是一种特殊的存储阵列。它通过将输入数据与CAM中存储的所有数据项同时进行比较,迅速判断出输入数据是否与CAM中的存储数据项相匹配,并给出匹配数据项的对应地址和匹配信息。CAM以其高速查找、大容量等特点而被广泛地应用于电讯、网络等领域。 本文介绍一种用Ve ..

[查看全文]

分频器的VHDL描述

2012-06-02

10

在数字电路中,常需要对较高频率的时钟进行分频操作,得到较低频率的时钟信号。我们知道,在硬件电路设计中时钟信号时非常重要的。 下面我们介绍分频器的VHDL描述,在源代码中完成对时钟信号CLK的2分频,4分频,8分频,16分频。 LIBRARYIEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IE ..

[查看全文]

一个简单的总线轮询仲裁器Verilog代码

2012-06-02

18

下面这个是以输入信号作为状态机的转移条件,写得比较冗余: // // Verilog Module demo1_lib.bus_arbitor.arch_name // // Created: //by - Newhand //in - Shanghai ZhangJiang //at - 20:39:41 2003-12-03 // using Mentor Graphics HDL Designer(TM) // ///////////////////////////////////////////////////////// ..

[查看全文]

基于FPGA的多路脉冲重复频率跟踪器

2012-06-02

12

摘要:在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟踪器,它解决了在密集信号环境下信号跟踪的实时性问题,减小了系统体积。经过实验验证,其各项指标均达到了设计要求。 随着高科技的迅速发展,现代战争已经不仅是传统意义战场上 ..

[查看全文]

基于Nios II软核的运动目标检测系统设计

2012-06-02

闫飞 胡宝霞

7

由监控中心网络服务器和多台视频主机组成的监控终端与摄像头视频服务器进行网络互联所组成的基于Internet技术的Client/Server体系结构的传统数字监控系统软、硬件要求较高,且使用专业化,局限了视频监控在孤立、分散以及对成本要求较苛刻的场合的应用。随着现场可编程逻辑门阵列(FPGA)的应用越来越广泛,基于FPGA的各种 ..

[查看全文]

Verilog-HDL仿真软件ModelSim的基本操作

2012-06-02

常晓明

15

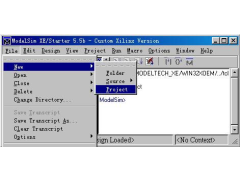

Verilog-HDL与CPLD/FPGA设计应用讲座 第 4 讲 Verilog-HDL仿真软件的基本操作 4.1 建立新的工程文件 4.2 一个最简单的仿真实例 在本讲以Xilinx WebPACK 4.1 ModelSim XE Starter为例,说明仿真软件的基本操作。 4.1 建立新的工程文件 启动Xilinx WebPACK 4.1 ModelSim XE Starter后,选中【File】菜单中的【New】菜单项, ..

[查看全文]

用FPGA实现非标码速向标准码速的调整

2012-06-02

33

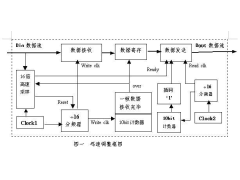

摘要:本文主要讨论了如何利用FPGA可编程芯片实现计算机输出的异步非标码速(如9.6k、19.2k、57.6k、115.2k、460.8k等)到其邻近的标准码速(如64k、128k、256k、512k)的调整,实现该数据与通用传输系统的适配,以便能进行远程监控。 关键词:码速调整 FPGA 一、概述 现在,利用计算机进行异地数据采集正应用到越来越 ..

[查看全文]

FPGA直接数字频率合成器的设计

2012-06-02

周俊峰 陈 涛

9

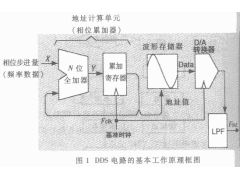

摘要:介绍了利用Altera的FPGA器件(ACEX EP1K50)实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。 关键词:直接数字频率合成(DDS) 现场可编程门阵列(FPGA) 直接数字频率合成(Direct Digital Fraquency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需要波形的一种新的频率 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

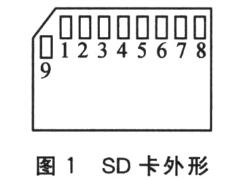

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317