ModelSim SE仿真Altera库的建立

2012-06-02

shemily

27

(注:最近自己准备做后仿真,到坛子里看看了,发现一开始建库就是一个很大的问题。为了便以自己学习也为了给大家省点事,我花了十来个小时整理了一些资料,全部资料来自edacn.net/bbs的ModelSim的〈库〉,在下面的资料中不能一一列出作者,请各位网友多多包涵。下面的资料是大家的成果。by CHY 07.04.05) 1. modelsim怎 ..

[查看全文]

自制wiggler-附原理图

2012-06-02

52

关于JTAG的原理,大家可以参考OPEN-JTAG 开发小组写的《ARM JTAG 调试原理》。JTAG、BDM 都比较类似,实际上是将仿真功能嵌入到芯片内部,接上比较简单的调试工具就可以进行开发了,省掉了高价的仿真器。 JTAG 调试用到了 TCK、TMS、TDI、TDO 和 TRST这几个脚。其中 TRST 是用来对 TAP controller进行复位的,它 ..

[查看全文]

关于modelsim的使用

2012-06-02

18

由于modelsim命令模式查看波形不方便,所以我们在仿真结束后查看波形进行查看,就需要存储波形。下面是网上的一点东西,给我的仿真带来了方便。 VCD system task calls in the Verilgsource code. .可以通过在源代码中添加语句来实现 initial begin $Dumpfile("./test.fsdb"); $Dumpvars(0,test); #60000000 $finis ..

[查看全文]

基于NIOS II内核的嵌入式SOPC开发板的实现

2012-06-02

14

随着大规模集成电路技术的进步和制造工艺水平的提高,嵌入式系统的开发变得日益复杂。传统的嵌入式系统设计方法已经不能适应当前嵌入式系统设计的需要。单个芯片容量的增大、功能的增加、体积的减小使得设计变得更加便利,同时也为嵌入式系统设计开发开辟了新的天地即片上系统(System on Chip,SoC)技术。 1 嵌入式系统的开 ..

[查看全文]

基于Nios软核CPU的uC/OS-II和LwIP移植

2012-06-02

李正军

18

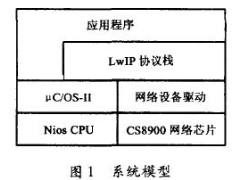

Altera公司推出的Nios软核CPU是一种可配置的通用精简指令集计算RISC(Reduced Instruction Set Computing)嵌入式处理器。它可以与各种外设相结合,构成一个定制的可编程片上系统SOPC(System on Programable Chip)。嵌入式实时操作系统uC/OS-II是一个非常优秀的实时操作系统RTOS(Real Time Operating System),其性能 ..

[查看全文]

VHDL语言程序配置EAB的研究

2012-06-02

何永泰

75

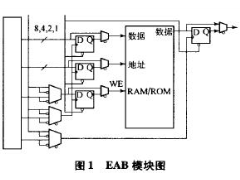

摘要: 在FPGA(现场可编程门阵列)的使用中,要将VHDL(甚高速集成电路硬件描述语言)编写的程序配置到EAB(嵌入式阵列块)单元中,会遇到许多问题,配置很难成功。根据配置EAB的经验,详细介绍了正确配置EAB的方法。 1、引言 FLEX10K器件是工业界第一个嵌入式的PLD(可编程逻辑器件),由于其具有高密度、低成本、低功率等特点,成 ..

[查看全文]

在Matlab中实现FPGA硬件设计

2012-06-02

江 霞

38

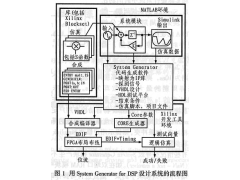

摘要 :System Generator for DSP是Xilinx公司开发的基于Matlab的DSP开发工具?熗?时也是一个基于FPGA的信号处理建模和设计工具。文章介绍了在Matlab中使用System Generator for DSP实现FPGA硬件设计的方法,同时给出了一个应用实例。 关键词 :Matlab;FPGA;System Generator;DSP 近年来,在数字通信、网络、视 ..

[查看全文]

基于MATLAB的DSP调试方法

2012-06-02

刘瑞华 潘建军

14

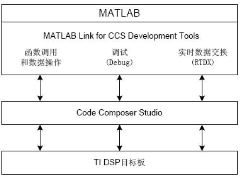

MATLAB 具有强大的分析、计算和可视化功能,利用MATLAB 提供的数十个专业工具箱,可以方便、灵活地实现对自动控制、信号处理、通信系统等的算法分析和仿真,是算法设计人员和工程技术人员必不可少的软件工具。 数字信号处理器(DSP)作为一种可编程专用芯片,是数字信号处理理论实用化过程的重要技术工具,在语音处理、图像 ..

[查看全文]

Verilog脉冲发生器程序

2012-06-02

万雪松

26

/*************************************************************************************** 实现功能简述 本模块主要功能是产生一个确定时钟周期长度(最长为256个时钟周期)的脉冲信号,可以自己设定脉冲长度,输出的脉冲信号与时钟上升沿同步 脉冲宽度 = pulsewide + 1 时钟周期; 输入一个启动信号后,可以产生一个 ..

[查看全文]

Verilog中模组(module)的概念

2012-06-02

10

模组(module)的概念 -------------------------------------------------------------------------------- Verilog中的基本单元是模组(module)。 模组代表一些可以用硬体实践的逻辑实体。 例如,一个模组可以是一个逻辑闸、一个三十二位元计数器、一个记忆体子系统、一个机算机系统或是一个用网路相连的多部电脑。 模 ..

[查看全文]

修改D1N4002的仿真参数(PSpice)

2012-06-02

12

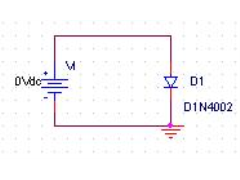

步骤一 绘出电路图、设置分析参数、存档及执行仿真 1、半导体元件均有其对应的仿真模型,所以我们可以根据自己的需求更改其模型型参数,以产生一个与元件有不一 样输入输出特性的二极管。首先新开一个项目D1N4002_1,然后如图1绘制电路图(也可以由D1N4002绘图页内复制 过来)。 图1 测量二极管V-I特性曲线的电路 2、然后用鼠 ..

[查看全文]

利用ModelSim SE6.0C实现时序仿真

2012-06-02

17

1) 打开一个工程文件。 2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。在右边出现的设置栏中将“Tool name”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

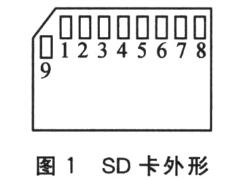

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317