ModelSim se完全编译Xilinx库文件

2012-06-02

20

什么是之前的老办法呢? Modlesim 仿真库的建立: 将Modelsim根目录下的modelsim.ini的属性由只读改为可写。 新建一个文件夹,比如library(为叙述方便,把它放在modelsim的根目录下)。D:/modelsim/library. 启动Modelsim,选择[File]/[chang Directory],选择D:/modelsim/library. 选择[File]/[New]/[library]命令,弹出[C ..

[查看全文]

Verilog交通灯控制器程序

2012-06-02

6

交通灯控制器 /* 信号定义与说明: CLK: 为同步时钟; EN: 使能信号,为1 的话,则控制器开始工作; LAMPA: 控制A 方向四盏灯的亮灭;其中,LAMPA0~LAMPA3,分别控制A 方向的 左拐灯、绿灯、黄灯和红灯; LAMPB: 控制B 方向四盏灯的亮灭;其中,LAMPB0 ~ LAMPB3,分别控制B 方向的 左拐灯、绿灯、黄灯和红灯; ACOU ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第7章 电应力工具)

2012-06-02

30

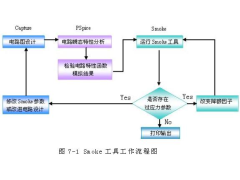

第7章 电应力(Smoke)工具的使用 电子电路在工作过程中,常因某(些)个元器件承受的热电应力超出其安全工作条件,降低其可靠性,严重地导致冒烟烧毁。因此,“冒烟报警”提高电路工作的可靠性,对一些安全性要求较高的电路(网络)采用降额设计已纳入电子工程师视野。本章结合电路实例简介可靠性、降额设计的基 ..

[查看全文]

debussy和modelsim协同仿真(VHDL)

2012-06-02

25

1、 编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。 2、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中 3、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录 4、 ..

[查看全文]

在Matlab中实现FPGA硬件设计

2012-06-02

江 霞

38

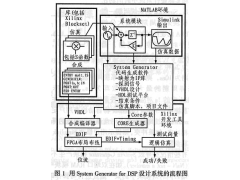

摘要 :System Generator for DSP是Xilinx公司开发的基于Matlab的DSP开发工具?熗?时也是一个基于FPGA的信号处理建模和设计工具。文章介绍了在Matlab中使用System Generator for DSP实现FPGA硬件设计的方法,同时给出了一个应用实例。 关键词 :Matlab;FPGA;System Generator;DSP 近年来,在数字通信、网络、视 ..

[查看全文]

Verilog HDL设计练习进阶(九)

2012-06-02

10

练习九.利用状态机的嵌套实现层次结构化设计 目的:1.运用主状态机与子状态机产生层次化的逻辑设计; 2.在结构化设计中灵活使用任务(task)结构。 在上一节,我们学习了如何使用状态机的实例。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是状态机套用状态机,从而形成树状的控制核心。这一点 ..

[查看全文]

LED显示屏灰度控制系统在Nios II中的实现

2012-06-02

陈昌龙 臧传晟

35

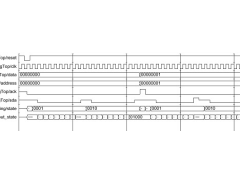

摘要:介绍了LED显示屏灰度的显示方法, 着重于显示屏设计中驱动控制方式的若干算法参数。根据这些算法参数,从系统的角度提出LED显示屏灰度控制完整算法。给出基于Cyclone ii芯片的Nios II系统的设计框图,并得到在Quartus II中的仿真结果。 1 系统设计 LED显示屏控制系统由视频采集系统、主控系统、数据分配电路和LED恒流驱动电 ..

[查看全文]

Verilog代码编写规范

2012-06-02

17

一. 强调Verilog代码编写风格的必要性。 强调Verilog代码编写规范,经常是一个不太受欢迎的话题,但却是非常有必要的。 每个代码编写者都有自己的编写习惯,而且都喜欢按照自己的习惯去编写代码。与自己编写风格相近的代码,阅读起来容易接受和理解。相反和自己编写风格差别较大的代码,阅读和接受起来就困难一些。 曾有编程大师 ..

[查看全文]

Verilog中模组(module)的概念

2012-06-02

10

模组(module)的概念 -------------------------------------------------------------------------------- Verilog中的基本单元是模组(module)。 模组代表一些可以用硬体实践的逻辑实体。 例如,一个模组可以是一个逻辑闸、一个三十二位元计数器、一个记忆体子系统、一个机算机系统或是一个用网路相连的多部电脑。 模 ..

[查看全文]

基于FPGA的高速数据采集系统接口设计

2012-06-02

黄伟,罗新民

16

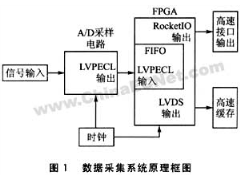

当前,越来越多的通信系统工作在很宽的频带上,对于保密和抗干扰有很高要求的某些无线通信更是如此,随着信号处理器件的处理速度越来越快,数据采样的速率也变得越来越高,在某些电子信息领域,要求处理的频带要尽可能的宽、动态范围要尽可能的大,以便得到更宽的频率搜索范围,获取更多的信息量。因此,通信系统对信号处理 ..

[查看全文]

分频器的VHDL描述

2012-06-02

10

在数字电路中,常需要对较高频率的时钟进行分频操作,得到较低频率的时钟信号。我们知道,在硬件电路设计中时钟信号时非常重要的。 下面我们介绍分频器的VHDL描述,在源代码中完成对时钟信号CLK的2分频,4分频,8分频,16分频。 LIBRARYIEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IE ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

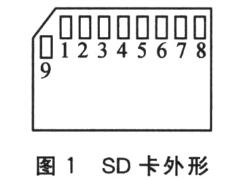

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317