CPLD开发板和FPGA开发板的区别

2012-06-02

抽烟的鱼

21

市面上尤其是学校里面可以看到Xilinx公司或者Altera公司各种不同的开发板,其实只有两个大类,CPLD开发板和FPGA开发板。尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点: ①CPLD更适合完成各种组合逻辑,FPGA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富 ..

[查看全文]

NiosII 快速入门(EDA软件的安装)

2012-06-02

8

Nios II是一个用户可配置的通用RISC嵌入式处理器。在这儿,我引用了Altera公司关于NiosII的官方介绍: Altera推出的Nios II系列嵌入式处理器扩展了目前世界上最流行的软核嵌入式处理器的性能,把Nios II嵌入到Altera的所有FPGA中,例如StratixII、Stratix、CycloneII,Cyclone、APEX,ACEX和HardCopy系列器件中,用户可以获 ..

[查看全文]

复用器重构降低FPGA成本

2012-06-02

13

摘要 本文介绍了一种新的能够降低FPGA实际设计20%成本的综合算法。该算法通过减少复用器所需查找表(LUT)的数量来实现。算法以效率更高的4:1复用器替代2:1复用器树。算法性能关键在于寻找总线上出现的复用器数量。新的优化方法占用一定的逻辑,这些逻辑由总线进行分担,从而减少了总线上每个比特位所需的逻辑。 1.引言 复 ..

[查看全文]

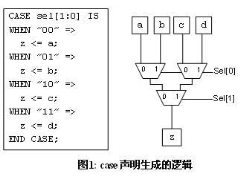

基于VHDL的异步串行通信电路设计

2012-06-02

李刚强

21

1 引 言 随着电子技术的发展,现场可编程门阵列 FPGA和复杂可编程逻辑器件CPLD的出现,使得电子系统的设计者利用与器件相应的电子CAD软件,在实验室里就可以设计自己的专用集成电路ASIC器件。这种可编程ASIC不仅使设计的产品达到小型化、集成化和高可靠性,而且器件具有用户可编程特性,大大缩短了设计周期,减少了设计费 ..

[查看全文]

可综合的Verilog FIFO存储器

2012-06-02

14

可综合的Verilog FIFO存储器 This example describes a synthesizable implementation of a FIFO. The FIFO depth and FIFO width in bits can be modified by simply changing the value of two parameters, `FWIDTH and `FDEPTH. For this example, the FIFO depth is 4 and the FIFO width is 32 bits. The input/output p ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第一章 安装)

2012-06-02

46

第1章 安装 OrCAD 10.3 Release1.1 OrCAD 10.3 Release安装建议的计算机配置1.1.1 OrCAD 10.3 Release 窗口操作系统OrCAD 10.3 Release可以执行在下列2 种Microsoft 窗口操作系统:(1)Windows 2000(SP4)(2)Windows XP Professional, or Windows XP Home Edition注:OrCAD10.3 Release已不再支持Windows NT 窗 ..

[查看全文]

怎样在NIOSII中操作PIO?

2012-06-02

GardenSu

14

运用NIOS II_IDE向导,在niosII_cyclone_1c20small下新建一个hello_led工程。 其中hello_led.c是这样写IO口的: IOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE, led); 首先在altera_avalon_pio_regs.h找到定义 代码 #include #define IORD_ALTERA_AVALON_PIO_DATA(base) IORD(base, 0) #define IOWR_ALTERA_AVALON ..

[查看全文]

Verilog代码编写规范

2012-06-02

17

一. 强调Verilog代码编写风格的必要性。 强调Verilog代码编写规范,经常是一个不太受欢迎的话题,但却是非常有必要的。 每个代码编写者都有自己的编写习惯,而且都喜欢按照自己的习惯去编写代码。与自己编写风格相近的代码,阅读起来容易接受和理解。相反和自己编写风格差别较大的代码,阅读和接受起来就困难一些。 曾有编程大师 ..

[查看全文]

FPGA等效门数的计算方法

2012-06-02

23

1. 把FPGA 基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA 基本单元的等效门数,然后乘以基本单元的数目就可以得到FPGA 门数估计值; 2. 分别用FPGA 和标准门阵列实现相同的功能,从中统计出FPGA 的等效门数,这种方法比较多的依赖于经验数据。 对于第一种方法,FPGA ..

[查看全文]

基于FPGA的FIR滤波器的实现

2012-06-02

郭继昌 向 晖 滕建辅 李香萍

23

摘 要: 提出了一种采用现场可编程门阵列器件 FPGA并利用窗函数法实现线性 FIR数字滤波器硬件电路的方案,并以一个十六阶低通 FIR数字滤波器电路的实现为例说明了利用Xilinx公司 XC4000系列芯片的设计过程。设计的电路通过软件程序进行了验证和硬件仿真,结果表明电路工作正确可靠,能满足设计要求。 关键词: FPGA FIR数字滤 ..

[查看全文]

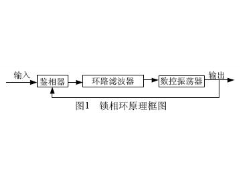

基于FPGA的逆变器全数字锁相环设计

2012-06-02

罗旭 占荣 康勇

36

摘要:文章设计了一种可应用于逆变器的、用FPGA 实现的二阶全数字锁相环(DPLL)。此锁相环用比例积分方法替代传统锁相系统中的环路滤波(LF),用相位累加器实现数控振荡器(DCO)的功能。具有输出相位连续、分辨率高等优点。分析了它的原理和结构,给出了关键部件的verilog 代码及仿真结果。仿真结果表明了设计的正确性 ..

[查看全文]

提高NC-Verilog仿真效率的技巧

2012-06-02

17

本文回顾了一些NC-Verilog的命令行选项,并说明这些选项如何影响仿真效率。同时,我们也展示了一些技巧,以帮助用户的NC-Verilog在最大效率下仿真一个设计和测试平台。 文中的命令行选项语法采用单步启动的方式(ncverilog +),这些选项也适合多步启动模式(ncvlog, ncelab, 或ncsim)。 安装最新发布的软件 首先确认你是否安 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

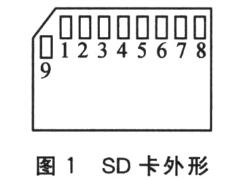

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317