基于MATLAB和Quartus II的FIR滤波器设计与仿真

2012-06-02

张园 王辉

32

在现代数字系统中,FPGA(现场可编程门阵列)以计算机为开发平台,经过设计输入、仿真、测试和校验,直至达到预期结果。本文使用MathWorks公司的MATLAB软件和Altera公司的FPGA开发软件Quartus II进行FIR滤波器的设计仿真,并给出了设计的一般步骤。该方法能够直观地检验滤波器的设计效果,提高设计效率,缩短设计周期。 ..

[查看全文]

Xilinx FPGA开发环境的配置

2012-06-02

风子心

24

一、配置Modelsim ISE的Xilinx的仿真库 1、编译仿真库: A、先将Modelsim安装目录C=Modeltech_6.2b下面的modelsim.ini改成存档格式(取消只读模式); B、在DOS环境中,进入Xilinx的根目录,然后依次进入bin,nt目录; C、运行compxlib -s mti_se -f all -l all -o C:Modeltech_6.2bxilinx_libs。 注意:需要根据你安装的modelsim目录 ..

[查看全文]

Quartus II中管脚上拉电阻(弱上拉)的设置方法

2012-06-02

Frank Wang

15

在使用Altera的FPGA时候,由于系统需求,需要在管脚的内部加上上拉电阻。Quartus II软件中在Assignment Editor中可以设置。具体过程如下: 1. 在菜单Assignments中选择Assignment Editor. 2. 在弹出的界面里选择I/O Features.找到Node. 3. 选择Node Finder选项后弹出如下界面 首先点击List 按钮,这里可以根据需求,列出仅 ..

[查看全文]

基于单片机的复杂可编程逻辑器件快速配置方法

2012-06-02

15

基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存配置数据。这些配置数据决定了PLD内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。由于SRAM的数据是易失的,因此这些数据必须保存在PLD器件 ..

[查看全文]

基于MATLAB的DSP调试方法

2012-06-02

刘瑞华 潘建军

14

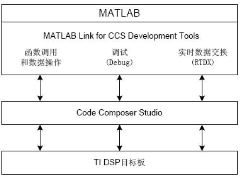

MATLAB 具有强大的分析、计算和可视化功能,利用MATLAB 提供的数十个专业工具箱,可以方便、灵活地实现对自动控制、信号处理、通信系统等的算法分析和仿真,是算法设计人员和工程技术人员必不可少的软件工具。 数字信号处理器(DSP)作为一种可编程专用芯片,是数字信号处理理论实用化过程的重要技术工具,在语音处理、图像 ..

[查看全文]

SDRAM接口的VHDL设计

2012-06-02

沙燕萍 曾烈光

22

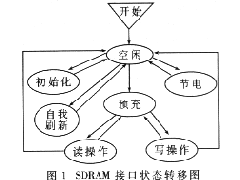

SDRAM接口的VHDL设计 RAM(随机存取存储器?犑且恢衷诘缱酉低持杏τ霉惴旱钠骷?,通常用于数据和程序的缓存。随着半导体工业的发展,RAM获得了飞速的发展,从RAM、DRAM(Dynamic RAM,即动态RAM)发展到SDRAM(Synchronous Dynamic RAM,即同步动态RAM),RAM的容量越来越大、速度越来越高,可以说存储器的容 ..

[查看全文]

ModelSim SE仿真Altera库的建立

2012-06-02

shemily

27

(注:最近自己准备做后仿真,到坛子里看看了,发现一开始建库就是一个很大的问题。为了便以自己学习也为了给大家省点事,我花了十来个小时整理了一些资料,全部资料来自edacn.net/bbs的ModelSim的〈库〉,在下面的资料中不能一一列出作者,请各位网友多多包涵。下面的资料是大家的成果。by CHY 07.04.05) 1. modelsim怎 ..

[查看全文]

浅谈VHDL/Verilog的可综合性以及对初学者的一些建议

2012-06-02

16

一、HDL不是硬件设计语言 过去笔者曾碰到过不少VHDL或Verilog HDL的初学者问一些相似的问题,诸如如何实现除法、开根号,如何写循环语句等等。在这个论坛上,也时常能看到一些网友提出这一类的问题。 对于这些问题,首先要明确的是VHDL和Veriglog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。HDL是Har ..

[查看全文]

奇偶校验器

2012-06-02

8

程序很简单,但是可以引申到很多小的细节 library IEEE; use IEEE.std_logic_1164.all; entity parity is port ( a: in STD_LOGIC_VECTOR (8 downto 0); b: out STD_LOGIC ); end parity; architecture parity_arch of parity is begin process(a) variable even:std_logic; begin even:='0'; for i in a'range loop if a(i)='1' then eve ..

[查看全文]

VHDL 编程的一些心得体会

2012-06-02

8

VHDL 是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。 与另外一门硬件描述语言 Verilog HDL 相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且 VHDL 具有设计重用、大型设计能力、 ..

[查看全文]

FPGA有限状态机模拟I2C总线设计

2012-06-02

潘小冬

20

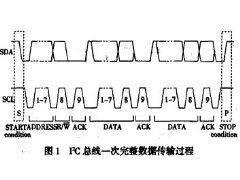

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模 ..

[查看全文]

CPLD开发板和FPGA开发板的区别

2012-06-02

抽烟的鱼

21

市面上尤其是学校里面可以看到Xilinx公司或者Altera公司各种不同的开发板,其实只有两个大类,CPLD开发板和FPGA开发板。尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点: ①CPLD更适合完成各种组合逻辑,FPGA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

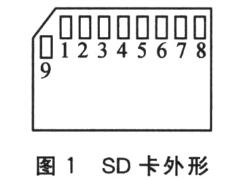

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317