利用Concept-HDL绘制原理图

打开Project Manager,选择concept HDL expert出现以下界面:

选择create Design Project,设定好必要的值,就创建好了一个工程。

进入原理图绘制环境,熟悉窗口和键盘操作后就可以绘制原理图了。这儿有一点值得注意:在psd工具包中原有的原理库图并不能直接和其中的物理封装很好的连接,也就是说,如果你使用了库里本来就有的器件原理图封装,你在试图向Allegro中转换的时候,是不能看到这个器件的物理封装的。这是由于原理图封装的Jedec Type找不到。但是有办法使原理图封装和物理封装相联系,只要将在library中所需的库拷贝到引导程序所在的my_lib目录下,然后用引导程序打开,将general标签中的Jedec Type属性改成我们自己所作的物理封装的.dra文件,然后存盘,再拷贝到library目录下我们自建的文件夹下面,这样这个器件的原理图封装和物理封装就都可以使用了。

使用Concept-HDL刚开始感觉不是很好用,但是在用了一段时间后会发现,它还是有自己独特的优点的,主要是可以用命令行来简化很多本来复杂的操作,鼠标的操作都要在选择了操作之后才可以对原理图有作用,这就避免了由于鼠标的误操作导致不经意的错误。

在每次保存的时候,Concept-HDL会自动地对页面查错,双击错误提示可以直接跳到发生错误的地方,很方便。除此之外,Concept-HDL有很多的工具可以使用,其中Check Plus是一个很好的差错工具。

从原理图到PCB图。在检查了原理图没有错误后,就可以向Allegro中导,File->Export Physical,出现以下窗口:

这个窗口可以先对原理图的进行封装,然后向PCB图中传送。Input Board和Output Board可以不一样。这样的倒有一个缺点:在向Allegro倒入之后,.brd文件就自动的保存,这样的话,如果原理图在改动后没有错误,但是改变了原来PCB图中已经画好了的线会产生DRC错误。而这个DRC错误,如果不是很明显的话,比较难发现,但是用Report可以很快的找到。但是由于现在的Allegro还没有返回功能,所以如果有错的话,会比较麻烦。

-

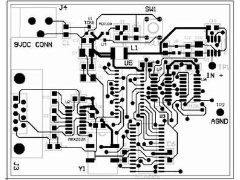

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

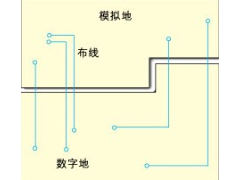

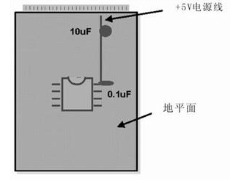

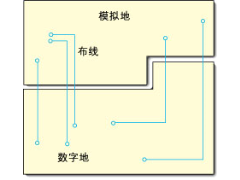

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

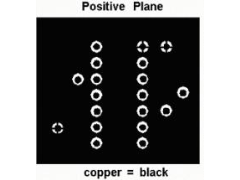

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

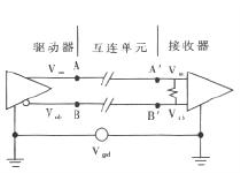

差分信号线的分析和LAYOUT2012年09月16日 144