FPGA 可编程全数字锁相环路的实现

2012-10-22

9

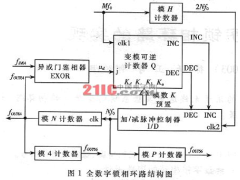

锁相环路已在模拟和数字通信及无线电电子学等各个领域中得到了极为广泛的应用,特别是在数字通信的调制解调和位同步中常常要用到各种各样的锁相环。锁相就是利用输入信号与输出信号之间的相位误差自动调节输出相位使之与输入相位一致,或保持一个很小的相位差。最初的锁相环全部由模拟电路组成,随着大规模、超高速数字集成 ..

[查看全文]

NIOS II网络驱动程序分析(1)

2012-10-21

柳军胜

11

网络是嵌入式应用的常备功能,在NIOS II中集成了UCOS II和LWIP,分析网络设备在NIOS II中的来龙去脉对学习NIOS II设备驱动程序有典型的意义。 设备的定义和系统设备联表管理。 1.驱动程序提供的freedev_rtl8019.h中定义一个freedev_rtl8019_if结构的全局变量dev #define FREEDEV_RTL8019_INSTANCE(name, dev) \ freed ..

[查看全文]

数字频率合成器的FPGA实现

2012-10-21

潘毅 李栋 龚建荣

9

摘要:介绍了DDFS的原理和Altera公司的FPGA器件ACEX 1K的主要特点,给出了用ACEX 1K系列器件EP1K10TC144-1实现数字频率合成器的工作原理、设计思路、电路结构和仿真结果。 1 概述 1971年,美国学者J.Tierncy,C.M.rader和B.Gold提出了以全数字技术,从相位概念出发直接合成所需波形的一种新的频率合成方法。限于当时的 ..

[查看全文]

测试向量(Test Bench)和波形发生器

2012-10-20

11

加法器源程序 module counter (count, clk, reset); output [7:0] count; input clk, reset; reg [7:0] count; parameter tpd_clk_to_count=1; parameter tpd_reset_to_count =1; function [7:0] increment; input [7:0] val; reg [3:0] i; reg carry; begin increment = val; carry = 1'b1; /* * Exit this loop when carry == ze ..

[查看全文]

三人表决器VHDL源程序

2012-10-20

7

--三人表决器(三种不同的描述方式) vhdl -- Three-input Majority Voter -- The entity declaration is followed by three alternative architectures which achieve the same functionality in different ways. ENTITY maj IS PORT(a,b,c : IN BIT; m : OUT BIT); END maj; --Dataflow style architecture ARCHITECTURE c ..

[查看全文]

在VHDL中实现高精度快速除法

2012-10-20

王飞

35

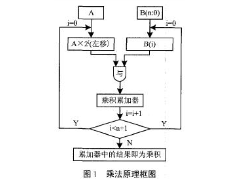

引言 在数字计算中,加、减、乘、除运算经常使用。在FPGA中,有加、减、乘、除的算法指令,但除法中除数必须为2的幂,因此无法实现除数为任意数的除法;而二进制除法算法中包含了减法、乘法、数的分解与合成、试商的判断等多种操作过程。因此,除法运算过程非常复杂,用VHDL编写除法运算很难实现。因此,作者根据二进制乘法 ..

[查看全文]

Modelsim的功能仿真和时序仿真

2012-10-20

13

FPGA 设计流程包括设计输入,仿真,综合,生成,板级验证等很多阶段。在整个设计流程中,完成设计输入并成功进行编译仅能说明设计符合一定的语法规范,并不能说明设计功能的正确性,这时就需要通过仿真对设计进行验证。在FPGA 设计中,仿真一般分为功能仿真(前仿真)和时序仿真(后仿真)。功能仿真又叫逻辑仿真,是指在不 ..

[查看全文]

Magafunction的用法

2012-10-18

11

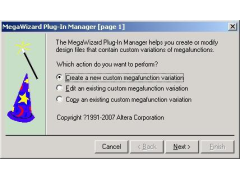

As design complexities increase, use of vendor-specific intellectual property (IP) blocks has become a common design methodology. Altera provides parameterizable megafunctions that are optimized for Altera device architectures. Using megafunctions instead of coding your own logic saves valuable design ..

[查看全文]

VHDL在高速图像采集系统中的应用设计

2012-10-18

11

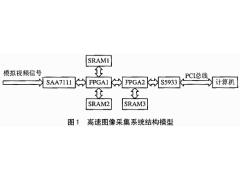

现代化生产和科学研究对图像采集系统的要求日益提高。传统的图像采集卡速度慢、处理功能简单,不能很好地满足特殊要求,因此,我们构建了高速图像采集系统。它主要包括图像采集模块、图像低级处理模块以及总线接口模块等。这些模块是在FPGA中利用VHDL编程实现的。高速图像采集系统主要用于视觉检测。视觉检测中图像处理的 ..

[查看全文]

VHDL设计举例:一个游戏程序

2012-10-17

12

--Copyright (c) 1993,1994 by Exemplar Logic, Inc.All Rights Reserved. -- -- This source file may be used and distributed without restriction -- provided that this copyright statement is not removed from the file -- and that any derivative work contains this copyright notice. -- ----------- -- --This is a syn ..

[查看全文]

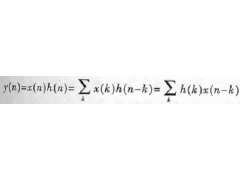

FIR数字滤波器分布式算法的原理及FPGA实现

2012-10-16

9

摘要: 在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘积-积结构相比,具有并行处理的高效性特点。详细研究了基于FPGA、采用分布式算法实现FIR数字滤波器的原理和方法,并通过Xilinx ISE在Modelsim下进行了仿真。 关键词: 分布式算法 DALUT FPGA FIR 数字滤波器正在迅速地代替传统的由R、L、C元件 ..

[查看全文]

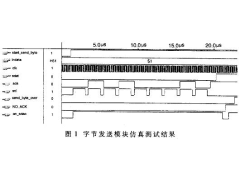

用Verilog HDL实现I2C总线功能

2012-10-16

11

摘要: 简述了I2C总线的特点;介绍了开发FPGA时I2C总线模块的设计思想;给出并解释了用Verilog HDL实现部分I2C总线功能的程序,以及I2C总线主从模式下的仿真时序图。 关键词: I2C总线 FPGA Verilog HDL 时序 开发FPGA时,利用EDA工具设计芯片实现系统功能已经成为支撑电子设计的通用平台,并逐步向支持系统级的设计方向发 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

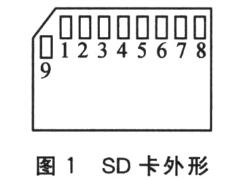

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300