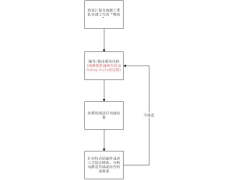

基于FPGA的电阻抗成像系统激励信号源

2012-10-28

王化祥 崔自强

33

电阻抗成像(Electrical Impedance Tomography,EIT)技术是一种廉价的无损伤探测技术,不使用放射源,对人体无害,可作为对患者进行长期、连续监护的医学监护设备. 在医学领域,考虑到患者的安全,激励信号源的电流应小于5 mA;不同人体组织的阻抗随频率变化的特性不同,因此要求激励信号源可以工作在单频、多频或扫频模式下 ..

[查看全文]

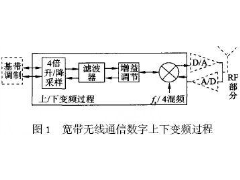

高速上下变频FIR滤波器的FPGA设计

2012-10-27

9

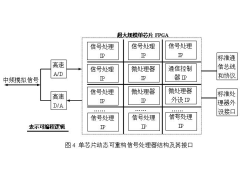

摘要: 针对宽带WLAN 收发器要求, 在单片FPGA 上设计实现了高速数字上下变频器和滤波器, 其中滤波器为80MHz 的40 阶FIR 滤波器, 可以设定工作在上变频或下变频方式。为了对FPGA 的资源占用量最小, 以便实现片上系统(SoC) 设计, 充分利用了上下变频过程中I,Q 数据流的特点, 仅用一套滤波器运算单元分时复用对I,Q 滤波, 同时详 ..

[查看全文]

VHDL上机手册(基于Xilinx ISE & ModelSim)

2012-10-27

23

1ISE 软件的运行及ModelSim 的配置 2创建一个新工程 3创建一个VHDL源文件框架 4利用计数器模板向导生成设计 *5仿真 6创建Testbench波形源文件 7设置输入仿真波形 *8调用ModelSim 进行仿真简介 9调用ModelSim 进行行为仿真(Simulate Behavioral Model) 10转换后仿真(Simulate Pose-Translate VHDL Model) 11调用ModelSim ..

[查看全文]

modelsim仿真学习笔记

2012-10-26

9

1、 仿真的目的 : 在软件环境下,验证电路的行为和设想中的是否一致。 2、 仿真的分类 : a) 功能仿真:在RTL层进行的仿真,其特点是不考虑构成电路的逻辑和门的时间延迟,着重考虑电路在理想环境下的行为和设计构想的一致性; b) 时序仿真:又称为后仿真,是在电路已经映射到特定的工艺环境后,将电路的路径延迟和门延迟考虑进对 ..

[查看全文]

ModelSim仿真库问题

2012-10-26

11

工作需要跑modelsim仿真,所用的环境是ise7.1+modelsim5.7CXE版本。设计需要在RTL code中增加DCM数字时钟单元,但是在自动调用modelsim仿真时出现error信息,说在库中找不到哪个DCM仿真文件。折腾了一会儿无果,赶快找专家解决问题,对方噼里啪啦三下五除二就将问题搞定,可惜当时没有看的太清楚,主要目的是用于: ..

[查看全文]

FPGA 在多制式视频转换系统中的应用

2012-10-25

11

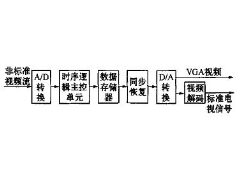

1 引言 目前, 在军事、工业和医学领域存在着大量的非标准视频系统, 其视频信号只能在专业的设备上才能播放和录制。而实际中广泛采用的是标准电视信号(PAL ,NTSC, SECAM) 或VGA 视频, 这就给这些领域内的观测监督和学术交流造成了许多困难。以医学信号为例, 目前, 国内医院很多科室的手术监控设备都是国外进口的一体式设备 ..

[查看全文]

用CPU配置FPGA(二)硬件设计

2012-10-25

7

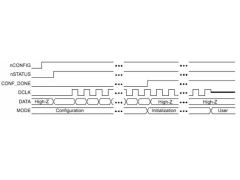

二. 硬件设计 1.配置基本原理 RAM-Based FPGA由于SRAM工艺的特点,掉电后数据会消失。因此,每次系统上电后,均需对FPGA进行配置。对于Altera的FPGA,配置方法可分为:专用的EPROM (Configuration EPROM)、PS(Passive serial 无源串行)、PPS(Passive parallel synchronous 无源同步并行)、PPA(Passive para ..

[查看全文]

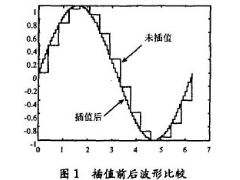

IIR滤波器matlab源程序

2012-10-25

128

(1)IIR一阶低通滤波器 P576 clear; fi=1;fs=10;Gc2=0.9; wc=2*pi*fi/fs; omegac=tan(wc/2); alpha=(sqrt(Gc2)/sqrt(1-Gc2))*omegac; a=(1-alpha)/(1+alpha); b=(1-a)/2; w=0:pi/300:pi; Hw2=alpha^2./(alpha^2+(tan(w/2)).^2); plot(w/pi,Hw2); grid; hold on; (2)一阶高通滤波器 P581 clear; fi=1;fs=10;Gc2=0. ..

[查看全文]

如何用synplify为maxplusII做综合

2012-10-24

12

如何用synplify为maxplusII做综合? 单个模块(文件)可用synplify(pro)综合,产生.edf文件,在max中编译,但是我用层次化设计时(即顶层模块调用许多底层模块)碰到了问题。max对synplify综合的顶层模块的.edf文件编译时报错。我把所有模块都用synplify综合后放在一个目录下,还是不行。如何解决? 1、综合时将层次结构消除 ..

[查看全文]

可编程片上系统(SOPC)设计技术

2012-10-23

徐欣

8

1. FPGA和SOPC概述 1.1 FPGA的特点及最新进展 嵌入式系统是一个面向应用、技术密集、资金密集、高度分散、不可垄断的产业,随着各个领域应用需求的多样化,嵌入式设计技术和芯片技术也经历着一次又一次的革新。虽然ASIC的成本很低,但设计周期长、投入费用高、风险较大,而可编程逻辑器件(Programmable Logical Device) ..

[查看全文]

基于FPGA 的高速实时FFT处理器设计

2012-10-22

周海斌 刘刚

12

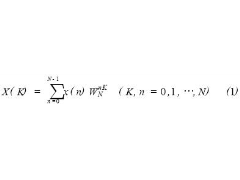

离散傅里叶变换(DFT) 是数字谱分析必需的变换工具。完成N 点DFT 运算约需N2 次乘法和N(N-1) 次加法,当N 较大时,运算量非常大,使其实际应用受到极大的限制。快速傅里叶变换(FFT) 采用递归型算法,利用旋转因子的周期性和对称性,将长序列DFT 分解为短序列DFT ,使总运算量减小1~2 个数量级,从而大大加快了运算速度。FFT 和 ..

[查看全文]

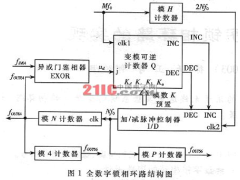

FPGA 可编程全数字锁相环路的实现

2012-10-22

9

锁相环路已在模拟和数字通信及无线电电子学等各个领域中得到了极为广泛的应用,特别是在数字通信的调制解调和位同步中常常要用到各种各样的锁相环。锁相就是利用输入信号与输出信号之间的相位误差自动调节输出相位使之与输入相位一致,或保持一个很小的相位差。最初的锁相环全部由模拟电路组成,随着大规模、超高速数字集成 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

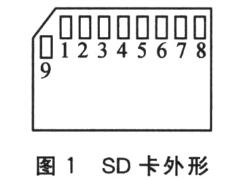

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300