二. 硬件设计

1.配置基本原理

RAM-Based FPGA由于SRAM工艺的特点,掉电后数据会消失。因此,每次系统上电后,均需对FPGA进行配置。对于Altera的FPGA,配置方法可分为:专用的EPROM (Configuration EPROM)、PS(Passive serial 无源串行)、PPS(Passive parallel synchronous 无源同步并行)、PPA(Passive parallel asynchronous 无源异步并行)、JTAG(不是所有器件都支持)。

本设计采用PS方式对FPGA进行配置,是基于如下几个方面的考虑:

1. PS方式连线最简单

2. 与Configuration EPROM方式可以兼容(MSEL0、1设置不变)

3. 与并行配置相比,误操作的几率小,可靠性高

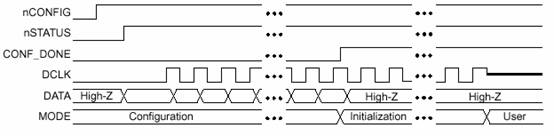

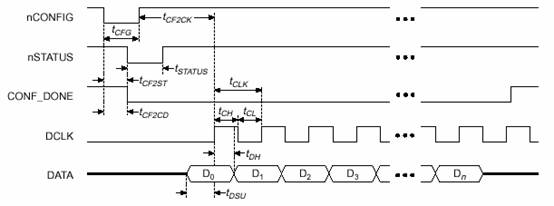

只需利用CPU的5个I/O线,就可按图 2所指示的时序对FPGA 进行PS方式的配置。

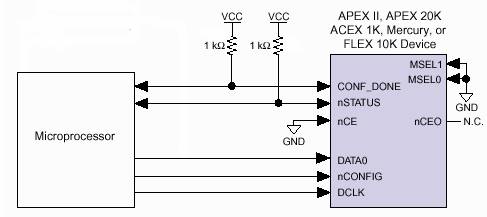

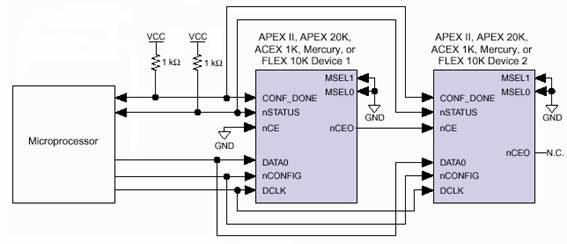

2.配置电路的连接

CPU仅需要利用5个I/O脚与FPGA相连,就实现了PS方式的硬件连接,具体信号见下表(信号方向从CPU侧看):

|

信号名 |

I/O |

说明 |

|

Data0 |

O |

configuration data |

|

DCLK |

O |

configuration clock |

|

nCONFIG |

O |

device reset (a low to high transition starts the configuration within the device) |

|

Conf_done |

I |

Status bit (gets checked after configuration, will be high if configuration complete) |

|

nSTATUS |

I |

Status bit indicating an error during configuration if low |

图 3 PS配置单片FPGA的硬件连接

图 4 PS配置多片FPGA的硬件连接

3.配置操作过程

CPU按下列步骤操作I/O口线,即可完成对FPGA的配置:

1. nCONFIG="0"、DCLK="0",保持2μS以上。

2. 检测nSTATUS,如果为"0",表明FPGA已响应配置要求,可开始进行配置。否则报错。正常情况下,nCONFIG="0"后1μS内nSTATUS将为"0"。

3. nCONFIG="1",并等待5μS。

4. Data0上放置数据(LSB first),DCLK="1",延时。

5. DCLK="0",并检测nSTATUS,若为"0",则报错并重新开始。

6. 准备下一位数据,并重复执行步骤4、5,直到所有数据送出为止。

7. 此时Conf_done应变成"1",表明FPGA的配置已完成。如果所有数据送出后,Conf_done不为"1",必须重新配置(从步骤1开始)。

8. 配置完成后,再送出10个周期的DCLK,以使FPGA完成初始化。

注意事项:

1. DCLK时钟频率的上限对不同器件是不一样的,具体限制见下表:

|

型号 |

最高频率 |

|

ACEX1K、FLEX10KE、APEX20K |

33MHz |

|

FLEX10K |

16MHz |

|

APEXII、APEX20KE、APEX20KC |

57MHz |

|

Mercury |

50MHz |

2. 步骤7中FPGA完成初始化所需要的10个周期的DCLK是针对ACEX 1K和FLEX 10KE的。如果是APEX 20K,则需要40个周期。

3. 在配置过程中,如果检测到nSTATUS为"0",表明FPGA配置有错误,则应回到步骤1重新开始。

图 5 操作流程框图

4.实现在线升级

采用本模块的最大优点是可以实现单板FPGA的在线升级。要实现在线升级,单板设计必须考虑以下几个问题:

1. CPU的启动必须不依赖于FPGA,即CPU子系统应在FPGA被配置前可独立运行并访问所需资源。CPU对FPGA进行配置所需的资源很少,一般来说,仅RAM和BootROM的访问而已。

2. FPGA配置前(或配置过程中)必须保证控制的设备处于非工作态或不影响其他设备工作的稳定态。

3. 为了实现FPGA的在线升级,存放FPGA配置数据的存储器器必须是CPU可重写的,且此存储器应是非易失性的,以保证单板断电后,FPGA数据不需从后台重新获得。

具体过程

结合图6的实例,对FPGA在线升级作一具体描述。

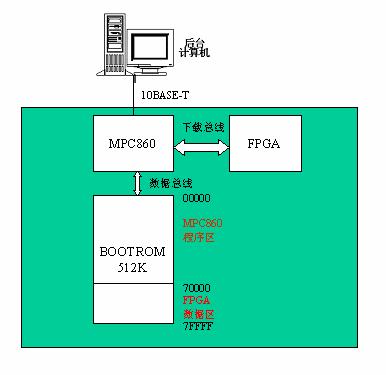

图6 FPGA在线升级

1. 使用编译和连接工具,将FPGA的第一个版本与MPC860的工作程序连接在一起,分别占用地址为0x70000-0x7FFFF和0x00000-0x6FFFF的存储空间。

2. 单板启动时,MPC860自动将0x70000-0x7FFFF的数据下载到FPGA中,完成FPGA配置。

3. 当FPGA需升级时,将新的RBF配置文件放在后台计算机中。

4. MPC860把BOOTROM的0x70000-0x7FFFF空间当作普通数据存储区,通过后台将新的RBF配置文件放在0x70000-0x7FFFF中。

5. MPC860调用BOOTROM中的FPGA配置子程序,对FPGA从新下载数据,完成FPGA升级。

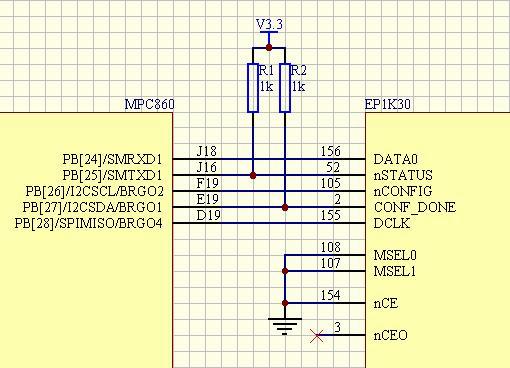

以MPC860和Altera EP1K30为例,电原理图如下:

图7 电原理图

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 191

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261