ModelSim+Synplify+Quartus的Altera FPGA的仿真与验证

2013-03-22

chenhongyi

标签:

3、自动布局布线(APR)

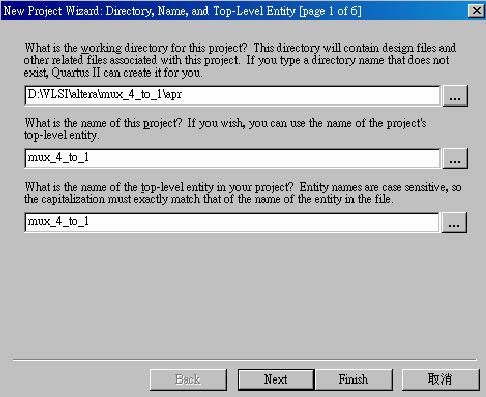

步骤一:开启Quartus II,然后建立一个Project。

※先点选File,再点选New Project Wizard…。

※设定Work Directory,Project Name与Top-Level Entity Name,再按Next。

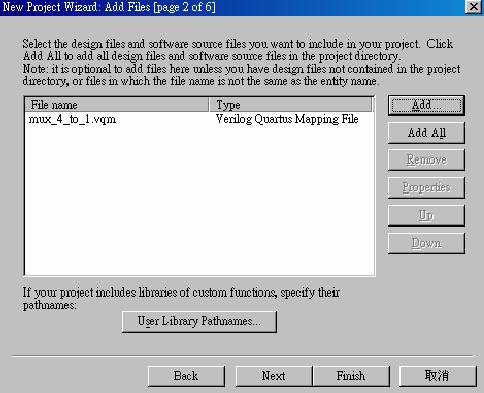

步骤二:加入设计文件。

※ 点选Add…,将Synplify合成出来的xxx.vqm加入,再按Next。

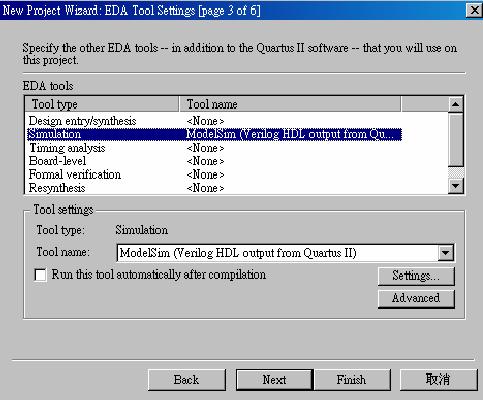

步骤三:设定相关的EDA Tools。

※在Tool Type点选Simulation,Tool Name点选ModelSim。

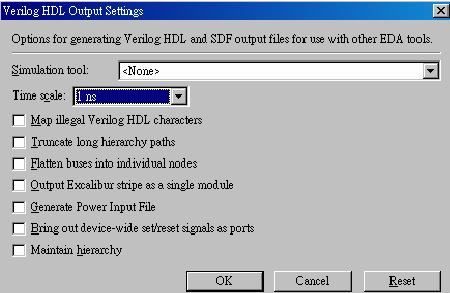

※ 点选Settings,将Time Scale设定为1 ns。

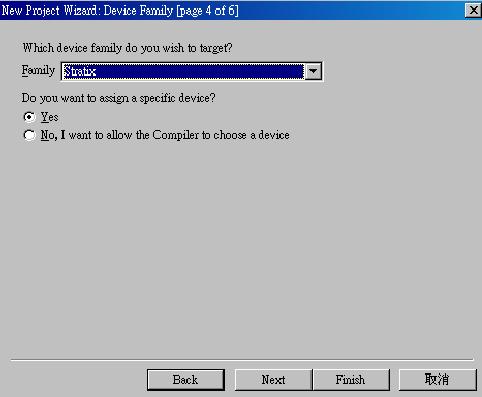

步骤四:设定Family。

※ 设定Family为Stratix,再按Next。

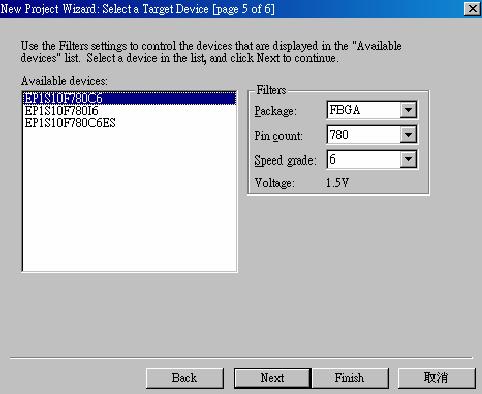

步骤五:设定Device。

※ 设定Device 为EP1S10F780C6,再按Finish,即可完成Project的设定。

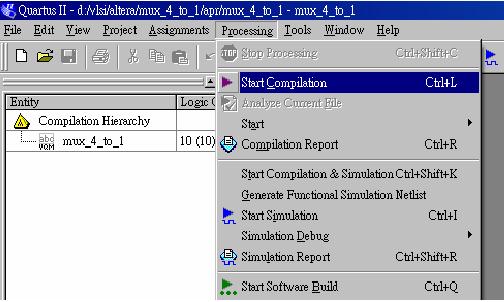

步骤六:编译。

※ 点选Processing → Start Compilation,即可开始编译。

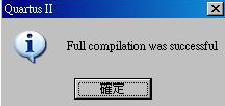

步骤七:完成编译。

※ 弹出下面窗口即代表编译完毕。

以上就是使用Quartus II对电路Netlist做APR的基本流程,并且利用设定仿真工具所产生的xxx.vo(Verilog Output File)与xxx.sdo(Standard Delay Output File)做后仿真。

可能会用到的工具/仪表

相关文章

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 192

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

热门文章

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261

章节目录