2、综合(Synthesis)

步骤一:打开Synplify Pro,然后建立一个Project。

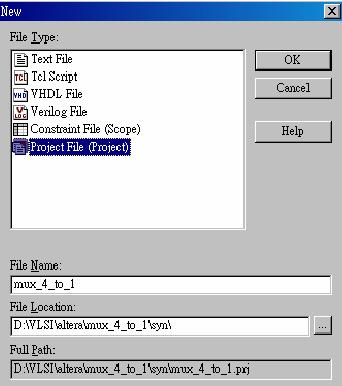

※先点选File,再点选New;

※选择Project File,并设定File Name与File Location;

步骤二:加入设计文件。

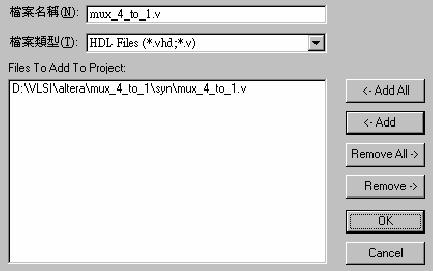

※ 点选欲加入的xxx.v,然后按Add,再按OK后就可以将档案加入。

步骤三:选择FPGA的Device 与其它相关设定。

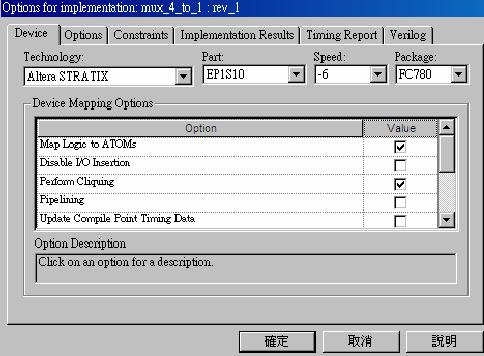

※先点选Project,再点选Implementation Options。

※在Device 的设定如下:Technology为Altera Stratix,Part为EP1S10,Speed 为-6,Package 为FC780。

※在Options 的设定是将FSM Compiler与Resource Sharing打勾。

※在Constraints的设定是将Frequency设定至100Mhz。

※在Implementation Results的设定是将Result File Name填入与电路模块相同的名称,而xxx.vgm这个文件会在QuartusII做APR时被使用。然后将下列两个选项打勾(Write Vendor Constraint File与Write Mapped Verilog Netlist)。

※在Timing Report的设定是将Number of Critical Paths与Number of Start/End Points都设为11。

※在Verilog里是将TOP Level Module填入与电路模块相同的名称,然后将 Use Verilog 2001打勾。

步骤四:综合(Synthesis)。

※点选RUN → Synthesize,最后出现Done!就是已经综合完毕。

步骤五:检查综合后的电路。

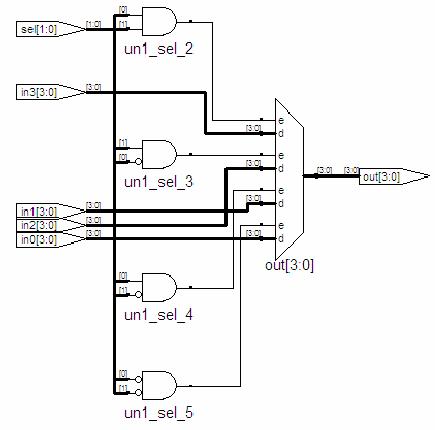

※先点选HDL Analyst,再点选RTL,最后点选Hierarchal View,画面会出现综合后的电路Netlist。

以上就是使用Synplify将HDL程序合成为电路Netlist的基本流程,值得注意的是,当你针对不同要求而设定的Constraints不同时,你就会得到不同的电路Netlist,所要付出的硬件代价也不同,这就需要大家多花点心思来了解其中的奥妙之处。

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 192

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261