8:一般在布线的时候,大家的DESIGN GRID设置为多大呀!

布兜

看具体情况。通常我设定5mils,这是因为我布线线宽为6mils,5+6大于10mils,那么我就很容易使线距就会自动为15mils。这样的线距距既符合我要求的线距,又能在布线时很容易的看出线间距均为15mils,很整齐的说。在密度大的地方,就设为1mils。

XiaoQY

我一般是用5MILS!

9:在那设置线的宽度呀

执行W6就可以了,哈!要多试验几次的,

布兜

如果你的走线宽度多数为6mils,那么在setup/design rules/default/clearance/trace width的recommended设为6mils就可以了。

Benbenzhuyi

临时改动用 W6,否则改Default值

10 那个换层命令怎么用

参数是不是分别代表起始层和要换到的层,那孔 VIA 不就有盲埋空的分别了,不是说最好成绩不要打这两种孔吗?

XiaoQY

L

改变当前层,如L2,则当前层为第二层!

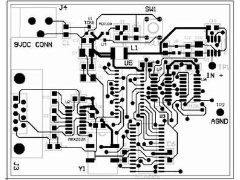

11 怎么叫从BGA 一个个的往外拉

yuan.lihua

中间的那些焊盘点都是电源或者地吗?那你怎么让他和电源层地层相连,是不是就是那个紫色的花空,那个怎么做呢,外面的都是信号的管脚吗?那每个都要外来,哈,你的线宽选择是多少呢?

XiaoQY

是呀!

花花绿绿的是电源和地!

有个地和电源层的!

只在打孔铺铜就可以的!

这线宽为5MILS的!

布兜

你的布局是你自己布的,还是参考模mode板?感觉不是很好。

像与BGA相连的那片贴装芯片,应该做适当的旋转,使得与BGA得连线最短。还有大贴片上面的那片小的,明明都与大贴片的左下脚的pin相连,可它偏偏在其上方。调整大贴片的方向要好些。

如果没有dome 作参考,布局就显得很重要。至少要把一组组的总线,主要元件在纸上画一画,大概那些总线走那一层,哪个位置、方向,大概多少条线,需要占多少位置。重要线如时钟线应如何走等等。如果板子大一点,劝你多花点时间布局。这样后面的工作会做到事半功倍,布局走线合理,板子完整性也会好些。

还有,首先你的引出BGA的管脚,就像xiaoQY贴得图那样。

值得一提的是,引线时一定要给电源、地留出打孔的地方,否则到最后,没地打孔哭都来不及。方法:view/nets把地、电源标注成某一颜色,连线时注意看是否有地打孔。

12 BGA 的连接地和电源

花孔的大小怎么来控制呢?

布兜

BGA 中间打过孔可能只有用 8/18,10/20 的 via,大了可能打不下。电源、地的 via 同一般过孔一样,你看到的十字花焊盘,在你定义了电源、地层,并分配网络后(setup/layer defintion),只要你打过孔到电源或地就会出现你看到的花焊盘。不过有个前提是你在setup/preferences/thermals定义了花焊盘。

XiaoQY

地和电源就打孔下到其层铺铜就好了呀!!!

不用连线的!!!

布兜

看来我没说明白,估计你是否没定义地和电源层?!

先不用铺铜,先定义电源、地层就可以了。

如果你定义了就这样操作,在连线状态下,右键/end via mode/end via,同时按下ctyl和鼠标左键,就会自动打过孔到你定义的层。

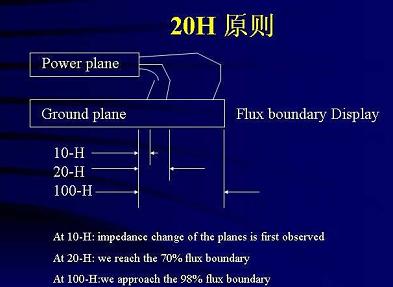

13 请教各位,这里的 20h 指的是什么呢?

betty

H 是指 power plane 与其最近的 ground plane 之实体距离。此距离包括 core 之厚度、prepreg filler 之厚度及 PCB 装配的隔离距离。假设此平面间的距离为 6mil,则得到 20-H 为 20X6=120mil. Power 平面应小于 ground平面120mil.

由于磁通的连接,RF电流存在于power plane的边缘.此种层间耦合作用称之为"fringing",通常仅见于高速PC

B.当使用高速逻辑用 clock 时,电源平面间会互相耦合 RF 电流且辐射至空间中.要减低此效应,所有电源平面

应较相邻的地平面小(依20-H rule).

电源分布临界效应发生在10-H左右,20-H代表约70%的通量边界(flux boundary),要达到98%的通量边界须1

00-H.

14 能问一下,过孔的大小

请问过孔的大小一般大家都设置为多大,还有在那设置过孔的大小!

布兜

这要看你的板子密度,一般我最小的用8/18或10/20mils,电源部分用大些32/50mils 左边是DRILLS的大小,右边是VIA的大小吗?

Lengcool

POWEPCB中 SETUP--》PAD STACKS--》VIA。我们用的标准孔是DRILL 为12MIL,DIAMETER的设置在START,INNER LAYERS,END中为24MIL,在电源层为40MIL。当有特殊要求时,就在DRILL 和DIAMETER两项改好了。多试

15是不是好象显示的线都很细呀

benbenzhuyi

不是,你敲热键 R 6 或 R 4试一下!

16 问个 EXPORT 的问题

输出的时候有些选择项目

unit 选择什么?

EXPAND ATTRIBUTE 要选择吗?

SECTION 选择什么?

布兜

unit绘图单位

section全选,点击select all就可以了。

EXPAND ATTRIBUTE 要选上

lengcool

我们是选SELECT ALL,UNIT中选CURRENT 就好了

17 各位线之间的间隔距离一般是多少呀

布兜

最好大于线宽,有空间当然越大越好了

你走6mils 的线,grid设为5mils,把snap to gird 选上,会很容易走出间隔相等的线。线据9mils,该满足要求的

lengcool

走线的线宽和线距一般是1:1,1:2有规律的,根据客户要求所定,当然既要美观又要效果好了,如用 6MIL线宽,可以把DISPLAY GRID设12MIL,G用6MIL

18 你们在布线的时候,是不是大多数的电容电阻最后加上去的,对吗?也就是说背面的元件

XiaoQY

晕~~~

走好后再加滤波电容???

修死你!

布兜

布局都完成后再布线,当然有个别的阻容器件位置可以在布线过程中作调整。

19:为什么我不能移动元件到 BOARDLINE 外呢?

好象初步布好局之后,想把元件移动到外面的话,没有办法移动,只能在 BOARDLINE 里面.请告诉我该怎么办

benbenzhuyi

暂时先把DRC关了!

XiaoQY

就是!

敲DRO

20 元件面、焊接面:敏感信号线

我们通常所说的,焊接面指的是那一部分!是背面吗?

Wood

通常说的焊接面是bottom layer,元件面指top layer,但是现在smd器件的广泛应用实际上两面都是焊接面也都是元件面了。

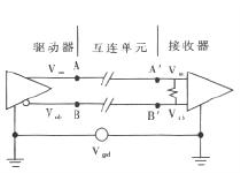

差分信号,指的是什么???有没有个确切的概念!

布兜

差分信号肯定有确切的概念,但我好像没法用通俗易懂的语言来说明。

差分线实际上是两条平行的耦合线,耦合线的两个导体电压幅度相等、相位相反。比如你经常在电路图上看到 TX+和 TX-就是一对差分线。因为差分线又阻抗要求,所以一对差分线线宽、线据都有具体要求。走差分线的好处是减少串扰,在传输不连续时减少损失。

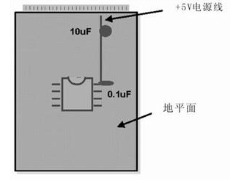

每个大功率器件应安装一个16uF 以上的电解电容或钽电容;并由其所放位置处负载的特性及纹波要求确定适当的容值,ESR 和ESL

这是因为什么呢?

布兜

当然是达到最好的滤波效果了。

21 电源电容的摆放是不是有什么讲究呢?

还有一个问题,电源的处理和不是先接一个大的10UF的电容,在接一个0.1UF的电容,是不是需要这两个电容摆放有没有什么讲究呢?

BILLWANG

没错,一般在POWER的进入端放一个大一些的E电容,每一个IC的电源端要加一个小瓷片电容.

-

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

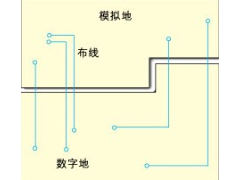

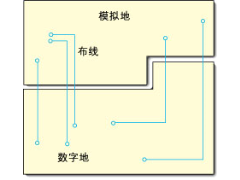

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

差分信号线的分析和LAYOUT2012年09月16日 144