debussy和modelsim协同仿真(VHDL)

2012-06-02

18

1、 编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。 2、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中 3、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录 4、 ..

[查看全文]

Verilog中模组(module)的概念

2012-06-02

6

模组(module)的概念 -------------------------------------------------------------------------------- Verilog中的基本单元是模组(module)。 模组代表一些可以用硬体实践的逻辑实体。 例如,一个模组可以是一个逻辑闸、一个三十二位元计数器、一个记忆体子系统、一个机算机系统或是一个用网路相连的多部电脑。 模 ..

[查看全文]

一种用VHDL设计嵌入式Web Server的方案

2012-06-02

13

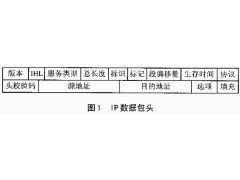

摘要:近几年嵌入式Internet开始迅猛发展,但绝大多数嵌入式Internet都使用微控制器和相应的软件来实现。本文介绍一种基于硬件来实现嵌入式Web Server的方案。该方案的核心思想是用VHDL语言来设计实现,并且用FPGA进行验证。 关键词:VHDL Internet协议 控制信息协议 数据报 最近几年随着Internet应用的迅猛发展,Intern ..

[查看全文]

基于VHDL语言的 IP 核验证

2012-06-02

13

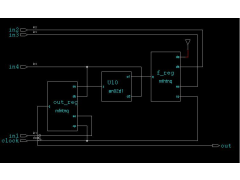

摘要:探讨了IP核的验证与测试的方法及其和VHDL语言在IC设计中的应用.并给出了其在RISC8框架CPU核中的下载实例 引言 在IC(integrated circuit.集成电路)发展到超大规模阶段的今天,基于IP(Intellectual Property,知识产权)核的IC设计及其再利用是保证SoC(system onchip,片上系统)开发效率和质量的重要手段。如果能对IP ..

[查看全文]

单片机多机冗余设计及控制模块的VHDL语言描述

2012-06-02

刘先昆 潘红兵

11

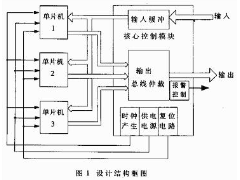

摘要:以三个单片机组成的系统为例介绍一种单片机多机冗余容错设计。阐述设计中关键的时钟同步技术和总线仲裁方法,给出控制模块的VHDL语言描述。 本文提出一种表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复杂的机间通讯协议实现系统重构,不太注重系统的实时性。本方 ..

[查看全文]

可综合的Verilog FIFO存储器

2012-06-02

10

可综合的Verilog FIFO存储器 This example describes a synthesizable implementation of a FIFO. The FIFO depth and FIFO width in bits can be modified by simply changing the value of two parameters, `FWIDTH and `FDEPTH. For this example, the FIFO depth is 4 and the FIFO width is 32 bits. The input/output p ..

[查看全文]

SystemVerilog语言简介

2012-06-02

39

SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、 接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。SystemVerilog由Accellera开发,它主要定位在芯片的 ..

[查看全文]

Verilog阻塞式赋值与非阻塞式赋值的分析

2012-06-02

nsun

13

在Verilog HDL中,有两种过程性赋值方式,即阻塞式(blocking)和非阻塞式(non-blocking)。这两种赋值方式看似差不多,其实在某些情况下却有着根本的区别,如果使用不当,综合出来的结果和你所想得到的结果会相去甚远。 Tip:所谓过程性赋值就是指在initial或always语句内的赋值,它只能对寄存器数 据类型的变量赋值。 阻塞式 ..

[查看全文]

Verilog脉冲发生器程序

2012-06-02

万雪松

24

/*************************************************************************************** 实现功能简述 本模块主要功能是产生一个确定时钟周期长度(最长为256个时钟周期)的脉冲信号,可以自己设定脉冲长度,输出的脉冲信号与时钟上升沿同步 脉冲宽度 = pulsewide + 1 时钟周期; 输入一个启动信号后,可以产生一个 ..

[查看全文]

VHDL 编程的一些心得体会

2012-06-02

6

VHDL 是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。 与另外一门硬件描述语言 Verilog HDL 相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且 VHDL 具有设计重用、大型设计能力、 ..

[查看全文]

VHDL设计举例:步进电机控制器

2012-06-02

20

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.ALL; USE IEEE.std_logic_arith.ALL; ENTITY step_motor IS PORT( f, p, d: INSTD_LOGIC:='0'; speed : inSTD_LOGIC_VECTOR(1 downto 0); coil : OUTSTD_LOGIC_VECTOR(3 downto 0) ); END step_motor; ARCHITECTURE behavior OF s ..

[查看全文]

SPI串行总线接口的Verilog实现

2012-06-02

孙丰军 余春暄

15

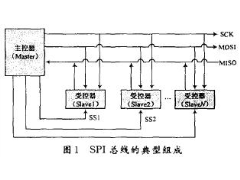

摘 要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。重点描述了SPI串行总线接口在一款 ..

[查看全文]

推荐文章

最新文章

热门文章