针对C语言编程者的Verilog开发指南

2012-06-02

13

本文举例说明了如何用软件实现脉宽调制(PWM),如何将该设计转换成一个可以在FPGA中运行的逻辑块,并能利用存储器映射I/O接口通过软件完成对该逻辑块的控制。通过理解本文讨论的概念和内容,没有太多硬件知识的软件开发人员也能掌握在FPGA上开发硬件的技能。 在不远的将来,嵌入式系统设计师将能够根据哪个更有利于解决设 ..

[查看全文]

Verilog HDL设计练习进阶(九)

2012-06-02

6

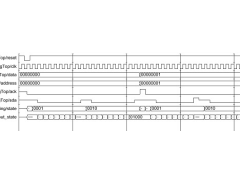

练习九.利用状态机的嵌套实现层次结构化设计 目的:1.运用主状态机与子状态机产生层次化的逻辑设计; 2.在结构化设计中灵活使用任务(task)结构。 在上一节,我们学习了如何使用状态机的实例。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是状态机套用状态机,从而形成树状的控制核心。这一点 ..

[查看全文]

一种基于移位寄存器的CAM的Verilog HDL实现

2012-06-02

8

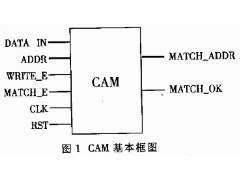

CAM(Content Addressable Memory,内容可寻址存储器)是一种特殊的存储阵列。它通过将输入数据与CAM中存储的所有数据项同时进行比较,迅速判断出输入数据是否与CAM中的存储数据项相匹配,并给出匹配数据项的对应地址和匹配信息。CAM以其高速查找、大容量等特点而被广泛地应用于电讯、网络等领域。 本文介绍一种用Ve ..

[查看全文]

Verilog中模组(module)的概念

2012-06-02

6

模组(module)的概念 -------------------------------------------------------------------------------- Verilog中的基本单元是模组(module)。 模组代表一些可以用硬体实践的逻辑实体。 例如,一个模组可以是一个逻辑闸、一个三十二位元计数器、一个记忆体子系统、一个机算机系统或是一个用网路相连的多部电脑。 模 ..

[查看全文]

Verilog HDL设计练习进阶(二)

2012-06-02

8

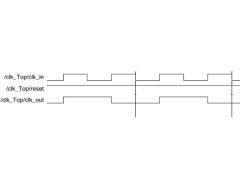

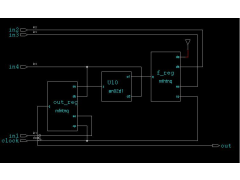

练习二. 简单时序逻辑电路的设计 目的:掌握基本时序逻辑电路的实现。 在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型,我们通常使用always块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个1/2分频器的可综合模型。 // half_clk.v: module half_clk( ..

[查看全文]

Verilog交通灯控制器程序

2012-06-02

5

交通灯控制器 /* 信号定义与说明: CLK: 为同步时钟; EN: 使能信号,为1 的话,则控制器开始工作; LAMPA: 控制A 方向四盏灯的亮灭;其中,LAMPA0~LAMPA3,分别控制A 方向的 左拐灯、绿灯、黄灯和红灯; LAMPB: 控制B 方向四盏灯的亮灭;其中,LAMPB0 ~ LAMPB3,分别控制B 方向的 左拐灯、绿灯、黄灯和红灯; ACOU ..

[查看全文]

Verilog阻塞式赋值与非阻塞式赋值的分析

2012-06-02

nsun

13

在Verilog HDL中,有两种过程性赋值方式,即阻塞式(blocking)和非阻塞式(non-blocking)。这两种赋值方式看似差不多,其实在某些情况下却有着根本的区别,如果使用不当,综合出来的结果和你所想得到的结果会相去甚远。 Tip:所谓过程性赋值就是指在initial或always语句内的赋值,它只能对寄存器数 据类型的变量赋值。 阻塞式 ..

[查看全文]

一个简单的总线轮询仲裁器Verilog代码

2012-06-02

15

下面这个是以输入信号作为状态机的转移条件,写得比较冗余: // // Verilog Module demo1_lib.bus_arbitor.arch_name // // Created: //by - Newhand //in - Shanghai ZhangJiang //at - 20:39:41 2003-12-03 // using Mentor Graphics HDL Designer(TM) // ///////////////////////////////////////////////////////// ..

[查看全文]

提高NC-Verilog仿真效率的技巧

2012-06-02

13

本文回顾了一些NC-Verilog的命令行选项,并说明这些选项如何影响仿真效率。同时,我们也展示了一些技巧,以帮助用户的NC-Verilog在最大效率下仿真一个设计和测试平台。 文中的命令行选项语法采用单步启动的方式(ncverilog +),这些选项也适合多步启动模式(ncvlog, ncelab, 或ncsim)。 安装最新发布的软件 首先确认你是否安 ..

[查看全文]

用Verilog-HDL做CPLD设计(组合逻辑电路的实现)

2012-06-02

李媛媛 常晓明

8

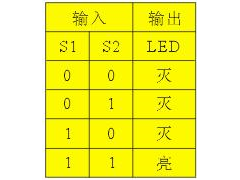

Verilog-HDL与CPLD/FPGA设计应用讲座 第 7 讲 用Verilog-HDL做CPLD设计 组合逻辑电路的实现 7.1 与非门的实现 7.2 2-1数据选择器的实现 7.3 2位二进制编码器的实现 7.4 1位数据比较器的实现 本讲中,我们通过由浅入深的实例来介绍组合逻辑电路在目标板上是如何实现的。 7.1 与非门的实现 首先,来实现一个用两个开关控制一个灯的 ..

[查看全文]

verilog的键盘源码keypad—有去抖功能

2012-06-02

11

下面是转的一个源码,俺没有细看,有兴趣的看看,讲讲如何 // author: Dandy Nee // mail:dandynee@yeah.net // module: HW KeyScan Module // version:0.1 // ************************** // all functions are provided as if okay // run at your own risk // ************************** // // problem:there is one keyva ..

[查看全文]

可综合的Verilog FIFO存储器

2012-06-02

10

可综合的Verilog FIFO存储器 This example describes a synthesizable implementation of a FIFO. The FIFO depth and FIFO width in bits can be modified by simply changing the value of two parameters, `FWIDTH and `FDEPTH. For this example, the FIFO depth is 4 and the FIFO width is 32 bits. The input/output p ..

[查看全文]

推荐文章

最新文章

热门文章