OrCAD复杂元件的多Part方式

2012-11-08

Joison

19

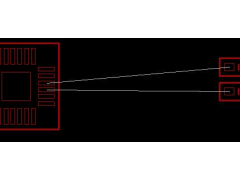

多PART绘制元件 多PAGE绘制原理图之一------利用多Part方式绘制复杂的元件 集成电路是越来越复杂,IC的pin也是越来越多。你准备像下面一样来绘制这个128pin的IC吗; 似乎128pin的IC绘制后看起来还不那么眼花,那么320pin的,更多pin 的呢。 看看下面这个 BGA,如果你用一个部分就把这个IC的原理图元件封装绘制完毕,我想即 ..

[查看全文]

Cadence 应用注意事项

2012-11-07

51

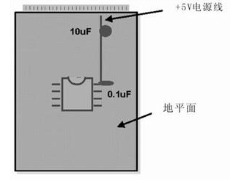

1、 PCB 工艺规则 以下规则可能随中国国内加工工艺提高而变化 1.1.不同元件间的焊盘间隙:大于等于 40mil(1mm),以保证各种批量在线焊板的需要。 1.2.焊盘尺寸:粘锡部分的宽度保证大于等于 10mil(0.254mm),如果焊脚(pin)较高,应修剪;如果不能修剪的,相应焊盘应增大….. 1.3.机械过孔最小孔径:大于等于 6mil(0 ..

[查看全文]

Allegro差分线的设定

2012-11-06

Asng Wang

20

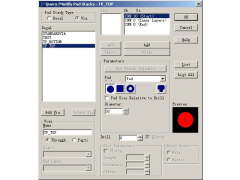

关于差分线的设定,Allegro 可以提供几种可行的方法,这里重点说明一种基本的,也是比较容易掌握的设定方法。以USB1 为例,要求 T/B:6/6;Inner:5/7.5;另外由于BGA 芯片的存在,BGA 区域T/B:4/4;Inner:4/7.5,所以需要在T/B、Inner 各提供Primary 和Neck 两种模式。如图: 步骤: 1. LogicAssign Differential Pai ..

[查看全文]

Allegro加工文件的生成过程

2012-10-31

9

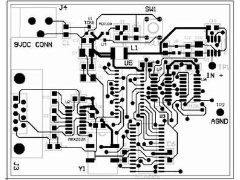

一直用PROTEL进行PCB画图,最近开始使用Allegro,个人感觉Allegro还是好使得多。由于是初次使用,所以对着教程一步步操作,就这样还是走了些弯路,画一个小板子折腾了两天。最后生成加工文件时,由于教程上说得不够清楚,也摸索了好一阵子。现将Allegro加工文件的生成过程小结以下,以供Allegro新手参考。 1、设定和生成底 ..

[查看全文]

Allegro List的用法

2012-10-29

23

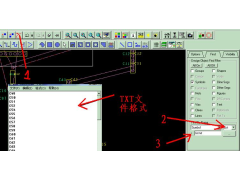

Allegro 中我们很感到不方便的就是批量处理多个位置不在一起的元件的时候,很麻烦。 其实Allegro 支持批量元件的处理,比如,多个元件同时删除/高亮/移动。。。等等,方法么,请看下文: 首先,假设我们有一个PCB,netin ok,现在我需要把若干元件同时删除(假设我们需要删除的元件已经在一个文本文件里面了),现在我们开始操作: ..

[查看全文]

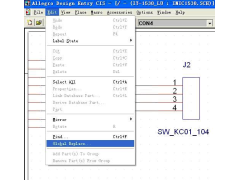

如何在allegro中更换元件封装

2012-10-27

无名小卒

16

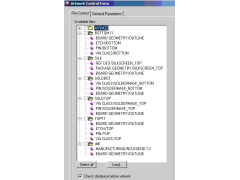

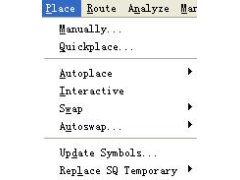

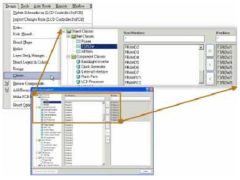

在allegro中,由于元件的封装出现了错误,需要修改元件封装,这时需要执行下面二步 1、第一步先在allegro中打开需要修改的元件封装dra,修改完后保存,如果是要换成另一个封装或者全部新建来更新,请保证元件名与原来一致,另外注意存放目录是原来的路径 2、关键的第二步,allegro自带一个更新功能,它在place菜单下 有一个Upda ..

[查看全文]

Allegro如何设定线长限制

2012-10-25

14

1,打开allegro setup---electrical constraint spreadsheet-->net-->routing-->relative propagation delay 2,鼠标右键system下面的文件名(brd 文件名)-->creat-->match group-->输入一个自定义的name(比如PCI1) 3,鼠标右键PCI1--membership-->match group-->选中所有需要长度设定的net到members 4,pin pairs 选 ..

[查看全文]

Allegro中电源层分割的步骤

2012-10-20

98

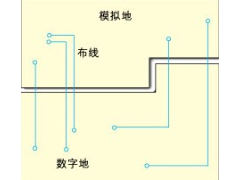

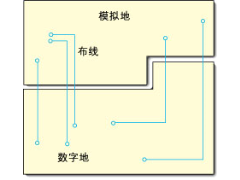

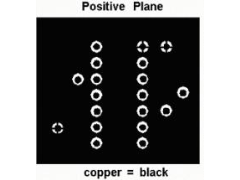

1. Click,在 Anti EtchVcc Layer,在紧贴Outline 画出一封闭区间,建议线宽采用40-60mil。此区间就是Negative Plane 的实际大小。如图: 2. Click , 在 Anti EtchVcc Layer, 切出各电源区域。建议线宽采用20-30mil. 3. 打开Vcc(Etch)层 ,选取菜单命令EditSplit PlaneParameter 15.1 以上版本此步骤可省略 4. 执行菜单命令Ed ..

[查看全文]

Cadence电路板设计文件旋转角度

2012-10-19

鲜飞

9

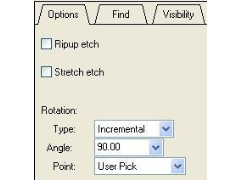

有时候出于编制生产设备程序的要求,例如插件机,需要将电路板设计文件旋转一个角度。但很多同事反映Cadence电路板设计文件旋转角度并不容易,经过我的仔细摸索,找到了解决办法,具体步骤如下: 1)电路板中锁定部分的解锁。先点击工具栏中的“Unfix”按钮,然后单击屏幕右侧的“Find”标签,点击&ld ..

[查看全文]

Allegro 布线规则设置说明

2012-10-15

lindawang117

31

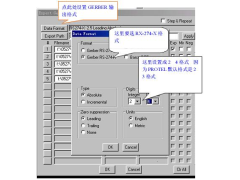

布线规则的设置通常包括线宽和线距两大部分。PCB 布线经常会要求对重要的信号线进行规则的设置。下面就以一主板Layout guide 为例部分说明之。 1. 首先是对整板未定义线规则的设置 ,如下表所示: Net Name Width Spacing Net Group Non-special Signal Inner layer: 4 Outer layer: 5 Inner layer: 4 Outer layer: 5 选择 打开set st ..

[查看全文]

Allegro 使用中的一些细节

2012-10-14

piaoxuer

31

为了便于大家察看pcb 版,我将Allegro 中遇到的一些细微的东西在此跟大家分享: 1、 焊盘空心、实心的显示 经常每个人都有自己视觉的习惯,有些人习惯空心焊盘而有些人则习惯实心的,当面对的板子和你自己的习惯矛盾时,可以用以下的方法来改变: 在菜单中选SetupÆDrawing Options….,会弹出一个对话框:在Display ..

[查看全文]

用allegro 布线的优点和缺点

2012-10-09

wangwz

10

记得刚毕业出来时就在某台商工作,用的就是allegro,从此上了贼船就下不来了~~。其实还用过pcad,protel,powerpcb(以下简称 3p,加上pads就4p了,呵呵~~)。至于mentor和cr5000就实在是没空去用了(有点难度)。除去mentor和zuken的软件不说, allegro相对于其它软件还是有其优势的。而贵公司的layout工作难度越大 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 60

-

高速PCB设计指南(三)2013年03月27日 154

-

PCB布线设计(二)2013年03月23日 45

-

混合信号PCB的分区设计2013年03月04日 30

-

高速PCB设计指南(六)2012年12月29日 30

-

PCB布线设计(一)2012年10月22日 13

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 49

-

常用电阻,电容,电感标称值2024年11月22日 92

-

PSPICE 的应用2013年04月06日 36

-

Protel DXP的电路仿真设计2013年04月04日 22

-

Gerber转protel的方法2013年04月04日 30

-

在PADS中添加表面型测试点2013年04月03日 49

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 384

-

Protel dxp等长走线2013年01月02日 333

-

Cadence 中添加工艺库文件步骤2013年01月16日 292

-

电气安全距离要求及分类2012年09月06日 273

-

Allegro铺铜的学习2012年12月05日 183

-

在ORCAD中整体修改网络名称2012年07月26日 177