一、 Allegro约束管理器(Front-Back)

一) Diff Pair

在Electrical Constraint Set工作薄中设置,约束集的值。

1、在NET下的Diff pair工作薄中选择一对NET,如下图,就创建了。

2、创建一个ECSets命名为ECSET1

3、Electrical Constraint Set下的每个工作薄中都有上图中的ECSET1的可设置项。加入需要的值。

1)、 Min/Max Propagation Delay中设置等长属性,改ns为mil并在PCB中User Preference中将DRC下选中pre_12.0_delay_rule。其它单位有点搞不懂。Pin Pair改为如上图。

2)、Impedance中设置阻抗控制

3)、Wiring中设置走线控制。

4)diff pair 中Neck项控制局部变细项。

5)、Primary Gap却是在NET的Diff Pair中不是全局控制,而是按组。

6)、Total Etch Length设置长度控制:

7)、在NET/Routing工作薄下,分配ECSets

其它:

Impedance中设置走线阻抗特征;

Wiring中设置走线的层等设置

完成设置。

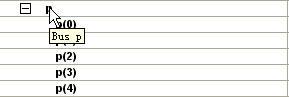

1、 BUS

这是原理图中的一个BUS,约束管理器不能创建BUS,但可以给它分配ECSets。参照Match Group。

2、 Match Group

是在Relation Propagation Delay中定义的NET、Pin_Pair组等。为等长设定。

Scope设置为Global(全板)Delta:Tolerance单位为mil,0:200是delta=0,

容差为正负200mil。最长的Pin Pair为等长范围。

在PCB中布线后上面的MG1不等长,U1.2:U2.2是Longest Pin Pair的目标,我们有专用等长工具来完成,点Route/Elongation By Pick,右键选Setup选相应的方式,Option中选层。

执行时可能出现不工作的情况,这时Chang Product再来就行了,该命令对无DRC错误的无效。结果如下:

3、执行分析

点击NET下左边工作薄相应项,在右边的Object列中点取一项按F9。开始分析。

4、交叉参考

在PCB中选择Display/Blank Rats/All,然后Display/Display Net在约束管理器中选择一网络在右键菜单中选择select该NET的Rats会出现在PCB中,HDL中相似。

-

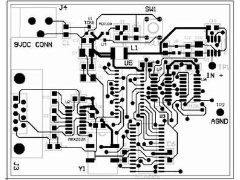

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

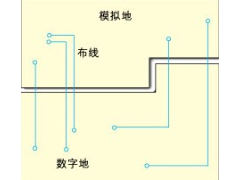

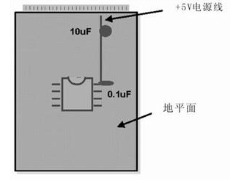

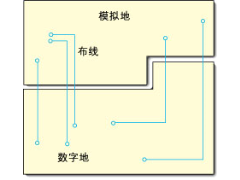

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

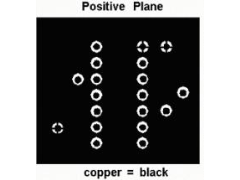

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

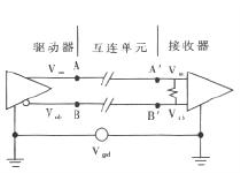

差分信号线的分析和LAYOUT2012年09月16日 144