1 LVDS信号的工作原理和特点

对于高速电路,尤其是高速数据总线,常用的器件一般有:ECL、BTL、GTL和GTL+等。这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的缺点,即功耗大。

新兴的CM0S工艺的低压差分信号(Low Voltage Differential Signal,简称LVDS)器件给了我们另一种选择。LVDS低压差分信号,最早由美国国家半导体公司(National Semiconductor)提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA (Telecommunication Industry Association/Electronic Industries Association)的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。

LVDS器件的工作原理如下:

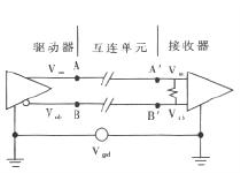

如图1所示,其中发送端是一个3.5mA的电流源,产生的3.5mA的电流通过差分线中的一路到接收端。由于接收端对于直流表现为高阻,电流通过接收端的100Ω的匹配电阻产生350mV的电压,同时电流经过差分线的另一路流回发送端。当发送端进行状态变化时,通过改变流经100Ω电阻的电流方向产生有效的'0'和'1' 态。

LVDS的特点是电流驱动模式,低电压摆幅350mV可以提供更高的信号传输率,使用差分传输的方式,输入信号只与2个信号的差值有关,可将共模干扰抑制掉,可以使信号的噪声和EMI都减少。综上所述,LVDS有以下主要特点:

- 低的输出电压摆幅(350mV);

- 差分特征是磁干扰相互抵消,消除共模噪声,减少EMI;

- 传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点。

2 LVDS信号在PCB上的设计

由LVDS信号的工作原理及特点可以看出:LVDS信号不仅是差分信号,而且还是高速数字信号;因此LVDS传输媒质不管使用的是PCB线对还是电缆,都必须采取措施防止信号在媒质终端发生反射,同时应减少电磁干扰以保证信号的完整性。只要我们在布线时考虑到以上这些要素,设计高速差分线路板并不很困难。下面将简要介绍LVDS信号在PCB 上的设计要点:

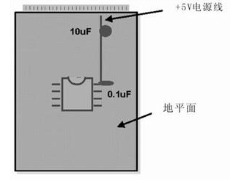

- 布成多层板。

- LVDS信号阻抗计算与控制。

- 紧耦合原则。

- 走短线、直线。

- 不同差分线对间处理。

- LVDS信号远离其它信号。

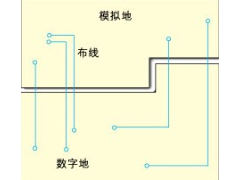

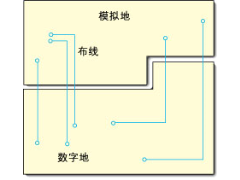

- LVDS差分信号不可以跨平面分割。

- 接收端的匹配电阻的布局。

- 匹配电阻的精度要求。

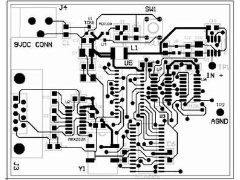

3、LVDS信号PCB设计实例

根据以上处理原则,简单介绍一块LVDS信号PCB设计实例,此板为16层多层印制板,叠层与板材(FR-4板材)关系如图6。

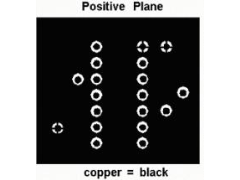

LVDS信号分别走在L1和L16层,L1的屏蔽层为G2,L16屏蔽层为G15(其中G2、G15是一完整的地平面),这样不但可以减少过孔数、线短,而且每个LVDS信号层都有完整的参考地平面相邻。

利用POLAR-SI6000计算表面微带差分走线:线宽6mils,线间距为6mils,阻抗理论计算值为99.1Ω。在生产过程中通过严格控制各种参数,利用CITS500S阻抗测试仪测试附连板的阻抗值范围为(95.6~106.8)Ω,完全符合阻抗控制要求。

4、结束语

在LVDS信号PCB设计上,我们要考虑的因素很多,不仅要考虑与其他信号相互间的影响,更关心是其自身阻抗的控制和线长控制等。

-

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

差分信号线的分析和LAYOUT2012年09月16日 144