我的仿真工作流程(Verilog/Modelsim+Debussy)

2012-06-02

25

这是献给大家的第二篇,文章详细说明了本人近一年来,自己摸索出来的一套仿真工作流程。接触过Modelsim这类软件的朋友可能都会感觉上手比较困难,原因有二:一、对仿真机制不了解,对基于source+testbench的工作流程不熟悉(大多数朋友接触FPGA仿真可能以waveform的方式);二、对软件的安装和使用不熟悉,Modelsim软 ..

[查看全文]

Verilog脉冲发生器程序

2012-06-02

万雪松

24

/*************************************************************************************** 实现功能简述 本模块主要功能是产生一个确定时钟周期长度(最长为256个时钟周期)的脉冲信号,可以自己设定脉冲长度,输出的脉冲信号与时钟上升沿同步 脉冲宽度 = pulsewide + 1 时钟周期; 输入一个启动信号后,可以产生一个 ..

[查看全文]

Verilog HDL设计练习进阶(三)

2012-06-02

7

练习三. 利用条件语句实现较复杂的时序逻辑电路 目的:掌握条件语句在Verilog HDL中的使用。 与常用的高级程序语言一样,为了描述较为复杂的时序关系,Verilog HDL提供了条件语句供分支判断时使用。在可综合风格的Verilog HDL模型中常用的条件语句有if…else和case…endcase两种结构,用法和C程序语言中类似。两者相 ..

[查看全文]

verilog设计经验

2012-06-02

10

一、组合逻辑 1、敏感变量的描述完备性 Verilog中,用always块设计组合逻辑电路时,在赋值表达式右端参与赋值的所有信号都必须在 always @(敏感电平列表)中列出,always中if语句的判断表达式必须在敏感电平列表中列出。如果在赋值表达式右端引用了敏感电平列表中没有列出的信号,在综合时将会为没有列出的信号隐含地产生一个透 ..

[查看全文]

Verilog HDL设计练习进阶(九)

2012-06-02

6

练习九.利用状态机的嵌套实现层次结构化设计 目的:1.运用主状态机与子状态机产生层次化的逻辑设计; 2.在结构化设计中灵活使用任务(task)结构。 在上一节,我们学习了如何使用状态机的实例。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是状态机套用状态机,从而形成树状的控制核心。这一点 ..

[查看全文]

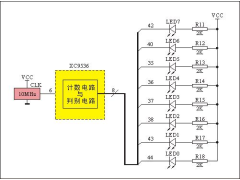

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)

2012-06-02

常晓明 李媛媛

22

Verilog-HDL与CPLD/FPGA设计应用讲座 第 8 讲 用Verilog-HDL做CPLD设计 时序逻辑电路的实现 8.1 闪烁灯的实现 8.2 流水灯的实现 8.3 可编程单脉冲发生器 在第七讲中,已经介绍了组合逻辑电路的实现。组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。时序逻辑电路则不同于它,其特点是:在任意 ..

[查看全文]

推荐文章

最新文章

热门文章