单片机汇编语言实现DES加密算法

2012-06-02

18

目前在金融界及非金融界的保密通信中,越来越多地用到了DES算法。DES(Data Encryption Standard)即数据加密算法,是IBM公司于 1977年研究成功并公开发表的。随着我国三金工程尤其是金卡工程的启动,DES算法在POS、ATM、磁卡及智能卡(IC卡)中被广泛应用,以此来实现关键数据的保密。如信用卡持卡人的PIN的加密传输、 ..

[查看全文]

Windows CE OAL层的结构与开发

2012-06-02

齐晓静 王卫东 王剑

7

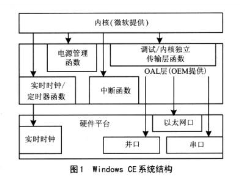

Windows CE微软针对嵌入式领域推出的一款全新的操作系统。之所以说它是一款全新的操作系统,是因为尽管Windows CE的UI非常接近其它的桌面版Windows操作系统,但是它的内核完全是重新写的,并不是任何一款桌面版Windows的精简版本。 Windows CE是一种支持多种CPU架构的操作系统,其中包括ARM、x86、MIPS和SHx,极 ..

[查看全文]

NiosII 快速入门(EDA软件的安装)

2012-06-02

6

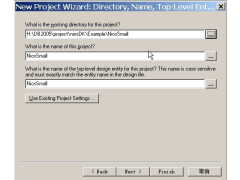

Nios II是一个用户可配置的通用RISC嵌入式处理器。在这儿,我引用了Altera公司关于NiosII的官方介绍: Altera推出的Nios II系列嵌入式处理器扩展了目前世界上最流行的软核嵌入式处理器的性能,把Nios II嵌入到Altera的所有FPGA中,例如StratixII、Stratix、CycloneII,Cyclone、APEX,ACEX和HardCopy系列器件中,用户可以获 ..

[查看全文]

nRF905模块和SPI接口的点对点无线通信系统

2012-06-02

李治龙 曾碧

13

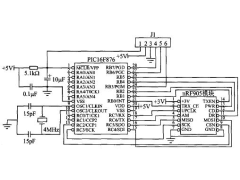

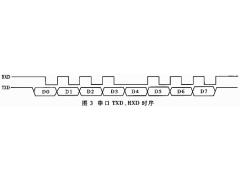

在某些环境监测、安防警报等环境下,不便进行有线线路的铺设,而采用无线数据通信方式。采用一般的无线传输方式时可能因为环境噪声大,干扰信号强而导致接收数据的准确性很低。针对这种情况,设计一种低成本、高准确率的无线数据传输系统—— 基于PIC16F876的SPI和nRF905模块的点对点无线通信系统。利用PIC1 ..

[查看全文]

基于单片机的复杂可编程逻辑器件快速配置方法

2012-06-02

12

基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存配置数据。这些配置数据决定了PLD内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。由于SRAM的数据是易失的,因此这些数据必须保存在PLD器件 ..

[查看全文]

VxWorks中的中断应用设计要点

2012-06-02

耿锐 王闵

9

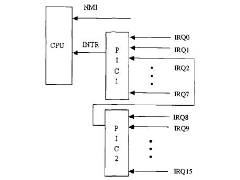

摘要:硬件中断处理是实时系统设计中的关键性问题,设计人员有必要对其作深入研究,以更好地满足开发工作需要。文中以VxWorks操作系统为软件平台,讨论了在实时系统中进行中断应用设计时要注意的一些问题。由于软硬件的相关性,选用广泛应用的X86架构的嵌入式汁算机为硬件平台,对PenriumCPU和计算机主板对硬件中断的管理机制 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第二章 OrCAD 10.3的结构)

2012-06-02

14

OrCAD10.3是OrCAD a Cadence product family 公司于2004年11月推出的电子设计自动化(EDA)软件系统。其中包括三个主要部分: 锁定元件信息系统的原理图输入器(Capture CIS); 模拟和混合信号仿真(PSpice A/D)和其高级分析(PSpice –AA); 印刷电路板设计(Layout Plus)形成Gerber文件可与Protel等PCB软 ..

[查看全文]

在Nexar上实现一个完整的嵌入式系统

2012-06-02

7

以下我们将结合一个实例来简要介绍一下如何在Nexar上实现一个完整的嵌入式系统设计过程。 首先:创建一个新的FPGA工程 1、选择菜单[menus]File>>New>>FPGA Project,在工程栏中将会显示新建的FPGA工程名,选择菜单[menus]File>>Save Project,在对话框中修改工程名称,然后Save。在工程栏中选择File View选项,在工程 ..

[查看全文]

分频器的VHDL描述

2012-06-02

7

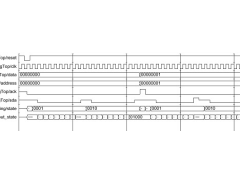

在数字电路中,常需要对较高频率的时钟进行分频操作,得到较低频率的时钟信号。我们知道,在硬件电路设计中时钟信号时非常重要的。 下面我们介绍分频器的VHDL描述,在源代码中完成对时钟信号CLK的2分频,4分频,8分频,16分频。 LIBRARYIEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IE ..

[查看全文]

Verilog HDL设计练习进阶(九)

2012-06-02

6

练习九.利用状态机的嵌套实现层次结构化设计 目的:1.运用主状态机与子状态机产生层次化的逻辑设计; 2.在结构化设计中灵活使用任务(task)结构。 在上一节,我们学习了如何使用状态机的实例。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是状态机套用状态机,从而形成树状的控制核心。这一点 ..

[查看全文]

利用Multisim 10中的MCU模块进行单片机协同仿真

2012-06-02

夏靖

6

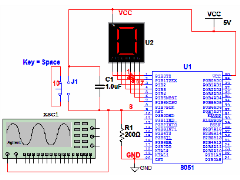

MCU(Microcontroller Unit)即单片机是大家都比较熟悉并常用的电子器件,由于其广泛的应用,所以用单片机设计电路是电子技术人员必备的技能。对于初学者,可以先从软件仿真入手。我们知道利用Proteus软件可以进行单片机的软件仿真,Multisim同样也可以。Multisim是基于SPICE的电路仿真软件,SPICE(Simulation Program ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

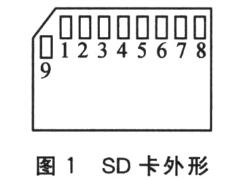

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300