PCB Layout 中的直角走线、差分走线和蛇形线

2012-06-02

月光王子

15

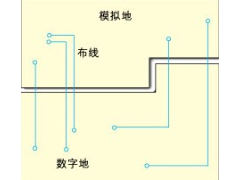

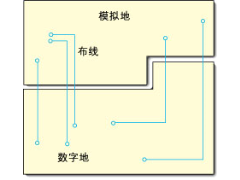

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线, ..

[查看全文]

电容在高速PCB设计中的应用

2012-06-02

21

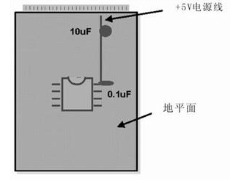

探讨高速PCB设计电容的应用。电容是电路板上不可缺少的一个部分,并且起到了至关重要的作用,探讨它具备至关重要的价值。您在设计中是否有这样困惑:我要用什么样的电容?需要多少这样电容?要如何放置这样的电容?带着这些疑问我们走入我们的正题笫—部分、电容的分类电容在电路的设计中从应用上进行分类,可以将电容分为四类 ..

[查看全文]

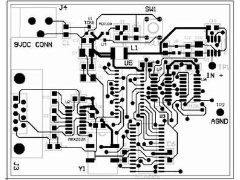

SPS PCB Layout细则

2012-06-02

23

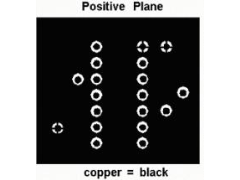

1.線路圖繪制 : a. 調出相應元件符號,連接繪制;并給其賦与相應之PCB Decal; b. 檢查网絡是否有錯;零件編號是否有重覆、遣漏;(存盤) c. 檢查無誤﹐轉net list to PCB;應無錯誤報告. 2.PCB圖繪制 : a. 檢查其封裝及帶极性元件的网絡是否正确; b. 1、用AUTO-CAD繪制PCB外框,轉成*.dxf文件到POWER PCB里去; § 注意:轉到POW ..

[查看全文]

高速PCB设计中的信号完整性分析问答

2012-06-02

27

一、您好:我看到很多SDRAM的数据、地址总线上都串接了小电阻(10欧姆到100欧姆); 1、这样做的主要目的是什么?串接的电阻阻值应该怎么来确定? 2、对于程序FLASH(比如NOR型的flash,access time=70ns)的数据和地址总线需要这样做吗? 不知道你的具体的拓扑结构,我觉得主要是限制信号的反射和过冲的。这要根据你 ..

[查看全文]

RF设计过程中降低信号耦合的PCB布线技巧

2012-06-02

14

新一轮蓝牙设备、无绳电话和蜂窝电话需求高潮正促使中国电子工程师越来越关注RF电路设计技巧。RF电路板的设计是最令设计工程师感到头疼的部分,如想一次获得成功,仔细规划和注重细节是必须加以高度重视的两大关键设计规则。 射频(RF)电路板设计由于在理论上还有很多不确定性,因此常被形容为一种“黑色艺术”, ..

[查看全文]

CS8900嵌入式以太网pcb设计中的几点注意事项

2012-06-02

16

(本文译自CS8900A PCB手册) 1.数字信号和模拟信号不能混合布线; 2.信号线不能走在cs8900a下面; 3.芯片 3对模拟电源、地对,4对数字电源、地对间都加0.1uF电容,连线尽可能短;连线一端接电容,另一端接网络; 4.两面铺铜,元件层的铺铜连到地网络上,焊接层的铺铜连到电源层; 5.传输线和接收线的终端匹配电阻和电 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 73

-

高速PCB设计指南(三)2013年03月27日 175

-

PCB布线设计(二)2013年03月23日 64

-

混合信号PCB的分区设计2013年03月04日 41

-

高速PCB设计指南(六)2012年12月29日 50

-

PCB布线设计(一)2012年10月22日 29

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 139

-

常用电阻,电容,电感标称值2024年11月22日 229

-

PSPICE 的应用2013年04月06日 52

-

Protel DXP的电路仿真设计2013年04月04日 38

-

Gerber转protel的方法2013年04月04日 51

-

在PADS中添加表面型测试点2013年04月03日 99

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 499

-

Protel dxp等长走线2013年01月02日 348

-

Cadence 中添加工艺库文件步骤2013年01月16日 304

-

电气安全距离要求及分类2012年09月06日 301

-

常用电阻,电容,电感标称值2024年11月22日 229

-

Allegro铺铜的学习2012年12月05日 225