Quartus II是Altera 公司单芯片可编程系统(SOPC) 设计的综合性环境,也是适合SOPC的最全面的设计环境。它拥有现场可编程门阵列(FPGA) 和复杂可编程逻辑器件(CPLD) 设计的所有阶段的解决方案。与原来的Max + plus II相比,Quartus II 在界面和功能上都发生了不少变化,除承接了原来Max + plusII的全部设计功能和器件对象外,还增加了许多新功能,如支持Max + plusII界面,支持RTLView 等,还增加了新的FPGA 器件系列,包括一些适用于SOPC开发的大规模器件。

本文以Quartus II 4.0 为设计平台,以FPGA 为核心,设计了一个具体数字系统即带计时器功能的秒表系统,使用Quartus II 4.0 的综合器和仿真器对系统进行了编译和仿真,得出了正确的仿真结果。

1秒表系统总体结构

要设计一个带计时器功能的秒表,计时范围为0.01 s~1 h ,计时器初值以min 为单位,最长计时时间为59 min。总体结构包括以下几个组成部分:

a) 显示屏,由6 个七段数码管组成,用于显示计时时间。

b) 输入数字键,用于设置计时器的计时时间(以min 为单位,不超过1 h) 。

c) START 键,用于启动秒表计时。

d) RESET 键,用于计时清零(复位) 。

e) ALARM 键,用于启动秒表的计时器功能。

f) 扬声器,在计时器计时结束时发声报警。

设计的总体结构图如图1 所示,主要显示了内部连接关系。

1.1秒表系统控制器

控制器外部端口如图1 所示。各端口的功能如下:

a) CLK为外部时钟信号,RESET 为复位信号。

b) 当KEY为高电平( KEY= 1) 时,表示用户按下数字输入键。

c) 当START-DOWN 为高电平时,表示用户按下“START”键。

d) 当ALARM-DOWN 为高电平时,表示用户按下“ALARM”键。

e) ALARM-END 为计数器送来的计时完成信号,为高电平时表示计时结束。

f) CLR 为提供给计数器的复位信号。

g) 当CLOCK-START 输出为高电平时,控制时钟计数器开始计时。

h) 当LOAD-NEW-TIME 输出为高电平时,控制寄存器下载新的计时时间。

i) 当SHOW-NEW-TIME 输出为高电平时,控制显示电路显示新的时间值。

控制器的功能可以通过有限状态自动机( FSM)的方式来实现。根据设计要求及端口设置,需要4 个状态来实现:

a) S0 :电路初态即等待状态。

b) S1 :秒表工作状态即正常计时状态。完成上述端口功能a 的工作,在状态S1 时用户按下START 键后进入此状态。

c) S2 :接收键盘输入状态。在状态S0 或状态S1时用户按下数字输入键后进入此状态,此时将接收到的键盘输入信息在七段数码管上显示。

d) S3 :计时器工作状态。在状态S2 时用户按下ALARM键后进入此状态,当计时完成后返回状态S0。

相应的状态转换及控制如表1 所示。

1.2秒表系统时间计数器

根据设计需要,要设计一个计时范围为0.01s~1 h 的秒表,命名为CLOCK。首先需要获得一个比较精确的计时基准信号,这里是周期为1/100 s 的计时脉冲。其次,除了对每一计数器需设置清零信号CLR输入外,还需在6 个计数器设置时钟使能信号,即计时允许信号ENA ,以便作为秒表的计时启停控制开关。

另外,为了完成计时器功能,需要一个控制减法计数功能的计时使能信号SET-TIME ,以作为计时器的启停控制开关。因此,秒表可由1 个分频器(用来提供计时基准信号) 、4 个十进制计数器(1/100 s ,1/10 s ,1 s ,1min) 以及2 个六进制计数器(10 s ,10 min) 组成。各部分组装完成后的时间计数器的外部端口如图1 所示。

各端口的功能如下:

a) CLR 为复位信号,CLK 为外部输入的时钟信号。

b) CLOCK-START 为高电平时,启动秒表计时。

c) LOAD-NEW-TIME 为高电平时,表示启动计时器计时。

d) SET-TIME 为接收到的计时初始时间。

e) OUT-CLOCK为输出给其他器件的时钟信号,时钟周期为1/100 s。

f) DOUTL 为输出给显示驱动器的低16 位信号。

g) DOUTH 为输出给显示驱动器的高8 位信号。

1.3接收键盘输入的缓冲器

缓冲器命名为KEYPAD。计时时间的输入利用两个按键分别代表1 min、10 min ,每按动一次,设置值加1 (相当于一个计数器,其最大值分别为9 、5) 。其外部端口如图1 所示。各端口的功能如下:

a) SCLR 为复位信号。

b) KEY1 、KEY2 为接收到的键盘输入信号,只有高电平和低电平两种状态。当输入一个上升沿时,计数加1 。

c) KEY为高电平时,表示有按键按下。

d) NEW-TIME 为转换后的计时时间。

1.4显示驱动器

本模块的功能是:当SHOW-NEW-TIME 端口输入信号有效(高电平) 时,根据NEW-TIME 端口输入信号(时间数据) 在DISPLAY 端口输出该信号。当SHOW-NEW-TIME 端口输入信号无效(低电平) 时,根据TIME 端口的输入信号判断输出。其外部端口如图1 中所示。各端口的功能如下:

a) CLR 为复位信号。

b) SHOW-NEW-TIME 为显示控制信号,为高电平时DISPLAY 的高8 位输出由端口NEW-TIME 引入的信号,为低电平时输出由TIME 引入的信号。

c) TIMEL 为由时间计数器引入的低16 位信号。

d) SOUND-ALARM 为高电平时,表示在计时器状态下计时结束。

1.5计时时间寄存器

本模块的功能是在时钟上升沿同步下, 根据LOAD-NEW-TIME 端口的输入信号控制TIME 端口的输出,当控制信号有效(高电平) 时,把NEW- TIME端口输入的信号值输出。其外部端口如图1 所示。各端口的功能如下:

a) CLR 为复位信号,对TIME 端口的输出进行异步清零复位。

b) LOAD-NEW-TIME 为输出控制信号,为高电平时,TIME 端口将输出由端口NEW- TIME 引入的信号(时间数据) 。

c) TIME 为输出端口,输出时间数据。

1.6整体组装

前面已经完成了秒表系统各个组成部分的设计,下面把这些部分组装起来,形成完整的总体设计。命名为TIMES ,其外部端口如图2 所示。

图2秒表系统的外部端口

各个输入输出端口的功能如下:

a) CLK为外部时钟信号,CLR 为复位信号。

b) START 为高电平时,表示用户按下START键,秒表计时启动。

c) ALARM 为高电平时,表示用户按下ALARM键,用于确定新的计时器时间设置。

d) SET-KEY1 和SET-KEY2 ,用于接收用户输入的时间数据。

e) DISPLAY 实际上表示了6 个七段数码显示管,用于显示时间。

f) SOUND-ALARM-OUT 为高电平时,驱动扬声器发声,表示计时结束。

2Quartus II4.0 的秒表系统整体仿真

以上完成了秒表系统的VHDL 设计。下面使用Quartus II4.0 对本设计进行编译和仿真。首先创建工程,使用文本编辑器输入本设计的所有模块的源程序,把TIMES.VHD 设为顶层文件。把本设计中的所有设计文件添加进工程后,先对每个模块进行编译纠错,然后进行全程编译,通过之后就可以进行仿真。每一部分的仿真从略,下面只说明系统的整体仿真波形。

系统工作在秒表功能时的仿真波形如图3 所示。

图3系统秒表功能的仿真波形

图中,START 为高电平时,表示用户按下了START键,秒表开始计时。这里把输出的DISPLAY 信号分成了6 组,每组代表秒表上的1 位。由于DISPLAY0代表的是最低位,也就是百分之一秒,所以显示不清晰。当接收到一个RESET 信号的高电平后时间清零,RESET 恢复低电平后,由于START 信号仍然为高电平,秒表重新开始计时。

系统工作在计时器功能时的仿真波形见图4 。

图4系统计时器功能时的仿真波形图

SET-KEY1 ,SET-KEY2 脉冲代表用户按下了数字输入键,有几个正脉冲就显示数字几。开始时START先变为高电平,系统开始秒表计时;图中所示0.21 s后SET-KEY1 来了正脉冲,秒表由显示驱动器驱动显示正在设置的计时时间。之后,ALARM 键变为高电平,计时器开始工作。由图中可看出,用户设置的计时时间为43 min ,按下ALARM 键后,系统开始倒计时。

3结束语

我们根据秒表系统的设计要求,把整个系统分成了几个模块来进行设计,并通过VHDL 语言完成了具体程序的编写,使用Quartus II 4.0 对系统进行了分析、综合,编译、仿真等工作,通过整体仿真,可以看出完成后的系统满足设计要求。整个设计充分利用了Quartus II4.0 的设计优势,简洁灵活,便于修改。

-

一款高温报警电路2024年11月13日 81

-

可燃气体全自动点火器2012年09月22日 76

-

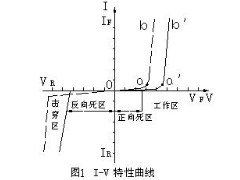

LED参数与特性2012年09月18日 118

-

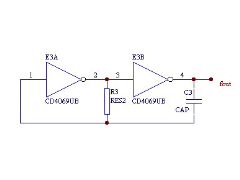

RC振荡电路的几种接法2012年09月10日 221

-

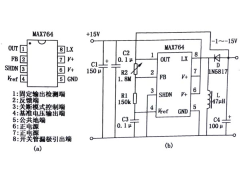

MAX764极性反转电路2012年08月24日 47

-

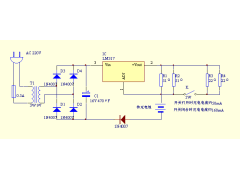

实用恒流充电器2012年08月18日 175

-

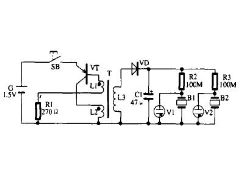

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4875

-

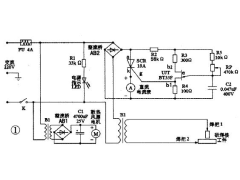

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499