5、 编写一个工程RTL 源码的Testbench 文件,用于作为仿真激励(具体如何编写清参考相关数据文档资料)。这个实例的testbench 如下:

module vtf_test;

// Inputs

reg clk;

reg rst_n;

// Output

wire div;

modelsim_test u1(

.clk(clk),

.rst_n(rst_n),

.div(div)

);

initial begin

clk = 0;

forever

#10 clk = ~clk; //产生50MHz 的时钟

end

initial begin

rst_n = 0;

#1000 rst_n = 1; //上电后1us 复位信号

#1000;

$stop;

end

endmodule

将该文件命名为tb_test.v,保存到3 提到的文件夹下。

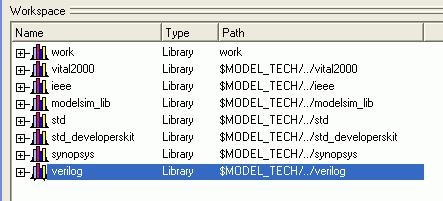

6、 在wokspace 的library 面板的空白处单击右键,选择“new”→“library”

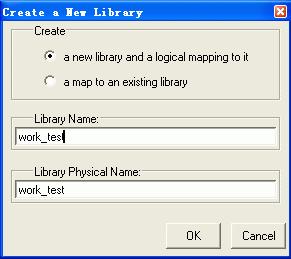

在新弹出界面中做如下设置,然后点击“OK”。

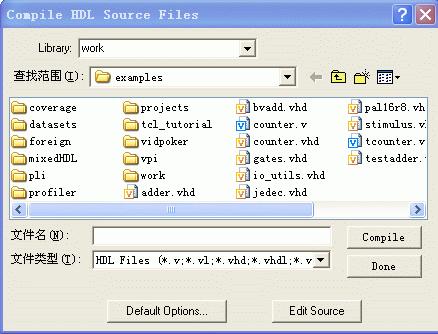

7、 启动ModelSim 软件,点击菜单栏的Compilecompile 命令,弹出如下界面:

Library 选择刚才新建的“work_test”,查找范围定位到我们3 提到的文件夹下。全选在该目录下可以看到的文件,点击Compile(注意该文件夹必须在全英文/数字路径下,否则会出错无法编译)。

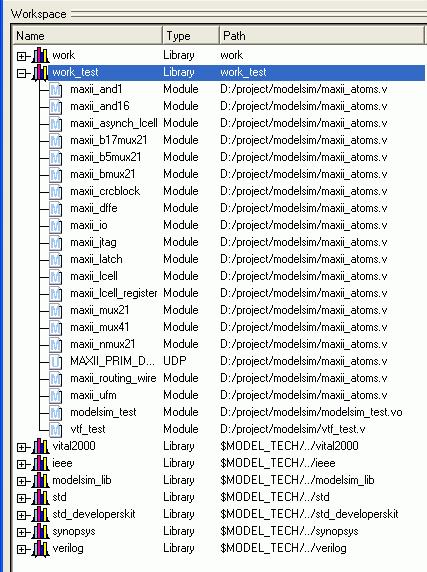

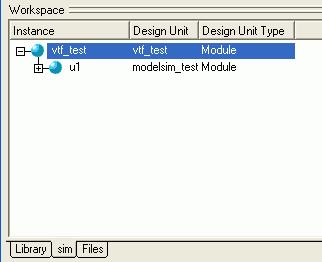

8、 我们回到wokspace 的library 面板,work_test 多处了下拉框,点击后如下:

我们右键单击vtf_test 文件,在弹出的菜单中选择Simulation

9、 执行上面的操作后,软件自动弹出wokspace 的sim 面板如下:

在vtf_test 栏单击右键,在弹出菜单中选择AddAdd to Wave。然后软件将弹出波形窗口。

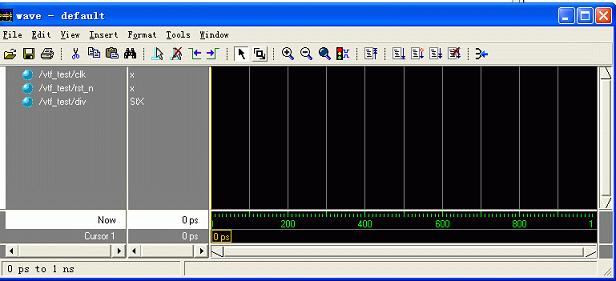

10、 波形窗口如下:

这时我们点击全速编译(一次不行,多点一次,工具栏倒数第三个按钮),

然后点击观看全部波形(放大缩小按钮后面一个蓝色按钮)。

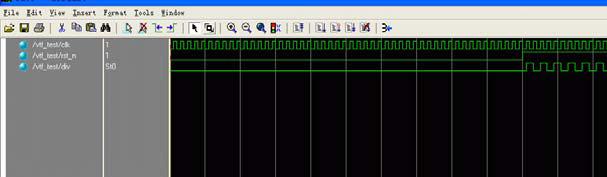

11、 仿真结果如下:

可以看到div 信号确实是clk 的二分频。呵呵,基本的操作就到此结束了。

modelsim 具体的功能使用方面有待大家慢慢琢磨,很容易上手的,大家加油!

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 192

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261