TESTBENCH 语法参考

always

module clock_gen;

reg clock;

//Initialize clock at time zero

initial

clock = 1'b0;

//Toggle clock every half cycle (time period = 20)

always

#10 clock = ~clock;

initial

#1000 $finish;

endmodule

forever

module synchronize;

//Example 2: Synchronize two register values at every positive edge of

//clock

reg clock;

reg x, y;

initial

begin

clock = 1'b0;

x = 1'b0;

y = 1'b0;

#100000 $finish;

end

always #5 clock = ~clock;

always #11 y = ~y;

initial

forever @(posedge clock) x = y;

endmodule

initial

module stimulus;

reg x,y, a,b, m;

initial

m = 1'b0; //single statement; does not need to be grouped

initial

begin

#5 a = 1'b1; //multiple statements; need to be grouped

#25 b = 1'b0;

end

initial

begin

#10 x = 1'b0;

#25 y = 1'b1;

end

initial

#50 $finish;

endmodule

repeat

//Illustration 2 : Data buffer module example

//After it receives a data_start signal.

//Reads data for next 8 cycles.

module data_buffer(data_start, data, clock);

parameter cycles = 8;

input data_start;

input [15:0] data;

input clock;

reg [15:0] buffer [0:7];

integer i;

always @(posedge clock)

begin

if(data_start) //data start signal is true

begin

i = 0;

repeat(cycles) //Store data at the posedge of next 8 clock

//cycles

begin

@(posedge clock) buffer[i] = data; //waits till next

// posedge to latch data

i = i + 1;

end

end

end

endmodule

-

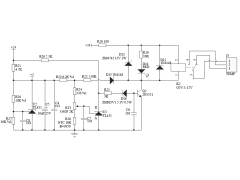

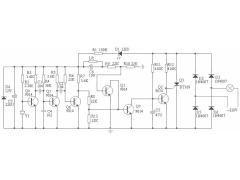

一款高温报警电路2024年11月13日 81

-

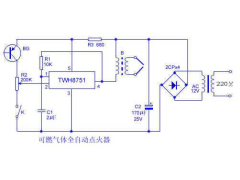

可燃气体全自动点火器2012年09月22日 76

-

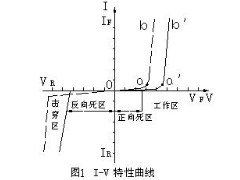

LED参数与特性2012年09月18日 118

-

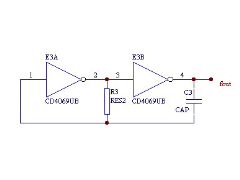

RC振荡电路的几种接法2012年09月10日 221

-

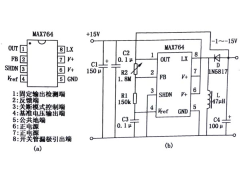

MAX764极性反转电路2012年08月24日 47

-

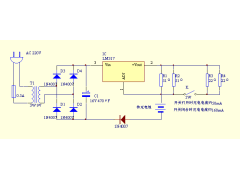

实用恒流充电器2012年08月18日 175

-

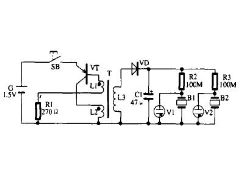

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4874

-

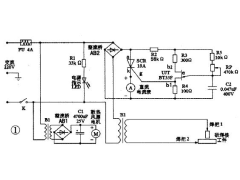

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

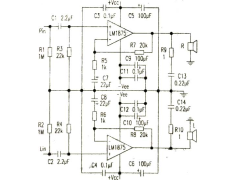

用LM1875替找TDA20302012年09月15日 777

-

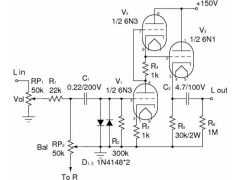

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

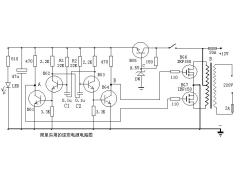

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499