在ORCAD中整体修改网络名称

2012-07-26

168

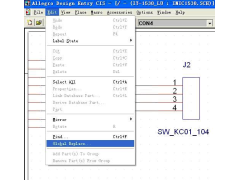

在ORCAD中整体修改网络名称 1, 使用整体属性编辑(查找与替换)功能: 如下图示:EDIT>GLOBAL REPLACE… 2,查找网络进行修改:(例如将12V修改为VCC12V) 如图示: 修改后 原12V已经修改为VCC12V WSLENG@163.COM

[查看全文]

OrCAD Capture 原理图对话框中英对照

2012-07-26

62

OrCAD常用文档类型 *.opj—项目管理文件 *.dsn—电路图文件 *.olb—图形符号库文件 *.lib—仿真模型描述库文件 *.mnl—网络表文件 *.max—电路板文件 *.tch—技术档文件 *.gbt—光绘文件 *.llb—PCB封装库文件 *.log*.lis—记录说明文件 *.tpl—板框文件 *.s ..

[查看全文]

在ORCAD的原理图中提取元件到库中

2012-06-27

QQ:3005626

28

大家都知道在POWERPCB 中,要提取一个封装到元件库中是一件很方便的事,只要右击SAVE TO LIBRARY 就可以了! 但是有时候我们也需要将ORCAD 中的元件放到库中,应该怎么做呢! 首先建立一个自己的库, 这个很简单这里就不详细介绍了! 如果我们要将下图中的某个元件放到上面的库里。 我们图中选取这个元件放到库中: 我们右 ..

[查看全文]

OrCAD Power PIN 的注意事項

2012-06-19

20

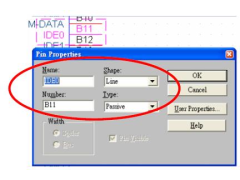

在 OrCAD Capture 建part时,其pin 的特性会影响后续在线路图的接线及转出的连线关系。 Part 的接点基本上可分 一般讯号PIN 与 电源讯号PIN 。 在使用时请特别注意其特性及差异。 一般讯号 PIN 指 Type 为 POWER 以外的一般讯号.需要接上 wire或port等才会有连线关系,或可用Place/No Connect宣告不接。 在同一颗 Part 中其 Pin na ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第8章 参数测绘仪工...

2012-06-02

11

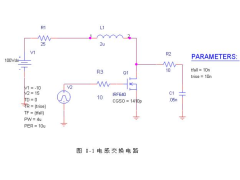

第8章 参数测绘仪(Parametric Plotter)工具的使用 参数测绘仪工具不但可以进行多种复杂参数功能的扫描,还可以在Plot/Probe中通过表格与绘图形式更美观和有效的分析扫描结果。用户可以在创建和参数测绘仿真电路时,运用参数测绘仪来进行设计和相关参数模型的分析(任何结合部分)。也可以说参数测绘仪工具是标准PSPICE参 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第4章灵敏度分析工具)

2012-06-02

17

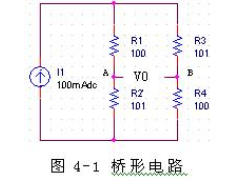

想要调用PSpice–AA进行电路优化设计,一般是先进行灵敏度(Sensitivity)分析:以便确定电路中对电路特性影响最大的关键元件参数进行优化。OrCAD9.2以前版本的灵敏度分析,由于有大量数据输出问题没有解决,故只局限于作直流灵敏度分析,置于直流工作点分析内。 直流灵敏度分析:虽然电路特性完全取决于电路中的元器 ..

[查看全文]

如何将OrCAD中的元件的Value传递到PADS 中

2012-06-02

Joison

39

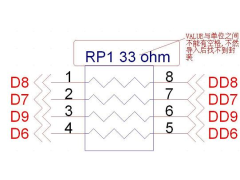

鉴于很多朋友反应,无法将OrCAD 中元件的Value导入到 PADS 中,所以下面我将做一下简单的介绍 (我使用的 OrCAD 10.5 版本,PADS是2005) 为每个元件指定PCB 封装,更详细说明 请参考 用Orcad做原理图,用PADS layout 特别要注意的是;添加 ,{Value} 注意 这里的逗号一定要是英文输入法下的逗号,Value这个字段要用大括号 ..

[查看全文]

Cadence产品的介绍

2012-06-02

12

Cadence公司是一家eda软件公司。成立于1988年。其主要产品线从上层的系统级设计到逻辑综合到低层的布局布线,还包括封装、电路版pcb设计等等多个方向。下面主要介绍其产品线的范围。 1、板级电路设计系统 。 包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第9章 仿真的故障排...

2012-06-02

30

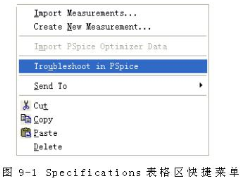

第9章 仿真的故障排除 在运行高级分析工具的过程中,由于操作失误、参数设置不合理等方面的原因,常常出现错误信息或者系统仿真不能运行等情况,用户往往得不到理想的分析结果,面对这些存在的难题,不能坐着发闷,要积极的解决问题。本章主要介绍运用故障排除分析工具解决存在问题的使用方法及高级分析中一般性故障的解决方 ..

[查看全文]

时序计算和Cadence仿真结果的运用

2012-06-02

余昌盛 刘忠亮

8

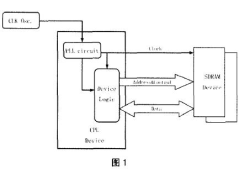

摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。 一、前言 通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在cadence仿真中,我们也获得了一系列的仿真结果,怎样把仿真 ..

[查看全文]

推荐文章

最新文章

热门文章