异步FIFO的VHDL设计

2013-04-06

9

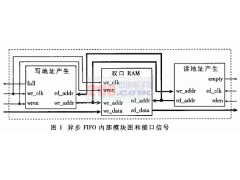

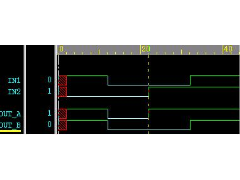

FIFO(先进先出队列)是一种在电子系统得到广泛应用的器件,通常用于数据的缓存和用于容纳异步信号的频率或相位的差异。FIFO的实现通常是利用双口RAM和读写地址产生模块来实现的。FIFO的接口信号包括异步的写时钟(wr_clk)和读时钟(rd_clk)、与写时钟同步的写有效(wren)和写数据(wr_data)、与读时钟同步的读有 ..

[查看全文]

C51与proteus怎样互联?

2013-04-06

15

proteus 的帮助文件里说,想要实现keil 与proteus 互联,要做以下几步: 1.设置TCP/IP协议(不清楚) 2.copy VDM51.DLL到 \C51\BIN 3.编辑C51 里tools.ini 文件, 加入:TDRV1=BIN\VDM51.DLL("PROTEUS VSM MONITOR 51 DRIVER) 4.keil 里设置: project-->options for project-->debug tab 5.选中use proteus VSM ..

[查看全文]

Xilinx DCM的使用

2013-04-06

8

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构 ..

[查看全文]

PIC 8位单片机芯片引脚功能

2013-04-06

18

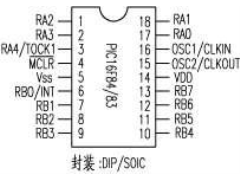

笔者读了本版有关PIC 8位单片机的产品性能和相应的封装引脚介绍后,认为对初学者而言还需了解各引脚符号的意义,才能进一步学习和使用它。笔者为此作相关的说明,以便和初学者共同提高。 一、关于I/O口符号 PIC单片机系列封装引脚最少的是8引脚(如PIC12C5XX和PIC12C6XX),多的可达84引脚(如 PIC17C76X),其中I/O(输入/输 ..

[查看全文]

Linux网络接口的源码分析

2013-04-06

李元佳

21

一.前言Linux的源码里,网络接口的实现部份是非常值得一读的,通过读源码,不仅对网络协议会有更深的了解,也有助于在网络编程的时候,对应用函数有更精确的了解和把握。 本文把重点放在网络接口程序的总体结构上,希望能作为读源码时一些指导性的文字。 本文以Linux2.4.16内核作为讲解的对象,内核源码可以在http://www ..

[查看全文]

在Modelsim se中创建altera仿真库

2013-04-06

20

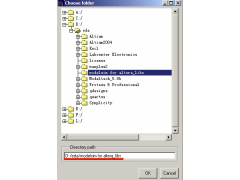

1. 路径选择 启动modelsim se仿真工具,在主窗口中选择【file】→【change directory】命令,将工作目录改变到你想存放仿真库的目录,点击【ok】. 2. 创建仿真库 在生窗口中选择【file】→【new】→【library】命令,在弹出的【create a new library】窗口中将选项【create】设置为【a new library and a logical ma ..

[查看全文]

VxWorks下在线升级技术

2013-04-05

15

看到有很多网友询问在VxWorks下如何实现在线升级,逐一答复了多次,还是没能说明白。因此决定把自己以前实际做的过程描述一下,希望能对大家有所帮助。如有不妥之处,请指出。 本人曾经在ppc860T, ppc850, pentium-pc104(加doc2000)的目标机上实现过。 1、首先,需要在目标机上实现文件系统,比如使用trueFFS,用dosF ..

[查看全文]

如何保证RTL设计与综合后网表的一致性

2013-04-05

王振国

7

文章简介:在超大规模数字集成电路的设计中,我们使用逻辑综合工具来完成从RTL设计到门级网表的转化。我们希望它综合出的门级网表与我们的RTL设计在逻辑和时序上完全一致。但是某些书写风格和设计思路却会造成两者不一致的情况,降低我们的工作效率。本文列举了三种RTL设计与综合后网表不一致的情况,并给出了解决方法.我 ..

[查看全文]

51单片机I/O口使用经验

2013-04-05

27

按常规,在51端口(P1、P2、P3)某位用作输入时,必须先向对应的锁存器写入1,使FET截止。一般情况是这样,也有例外。所谓IO口内部与电源相连的上拉电阻而非一常规线性电阻,实质上,该电阻是由两个场效应管并联在一起:一个FET为负载管,其阻值固定;另一个FET可工作在导通或截止两种状态(姑且叫可变FET)。使其总电 ..

[查看全文]

PIC C延时函数和循环体优化

2013-04-05

19

很多朋友说C中不能精确控制延时时间,不能象汇编那样直观。其实不然,对延时函数深入了解一下就能设计出一个理想的框价出来。一般的我们都用for(x=100;--x;){;}此句等同与x=100;while(--x){;};或for(x=0;x<100;x++){;}来写一个延时函数。在这里要特别注意:X=100,并不表示只运行100个指令时间就跳出循环。可以看看 ..

[查看全文]

VHDL 计数器源程序

2013-04-05

8

十五计数器library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; ENTITY fiveteencout IS PORT(clk,reset,enable : IN std_logic; count : OUT std_logic_vector(3 downto 0)); END fiveteencout; ARCHITECTURE counter OF fiveteencout IS SIGNAL count_int:std_logic_vector(0 to 3); BEGIN PROC ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 82

-

C99语法规则2024年11月16日 759

-

FreeRTOS 动态内存管理2024年11月12日 455

-

一款常用buffer程序2024年11月06日 96

-

1602液晶显示模块的应用2012年08月03日 196

-

GNU C 9条扩展语法2024年11月18日 274

最新文章

-

Corext-M3中断的具体行为2025年11月11日 45

-

优秀的字符串哈希算法-ELFhash2024年11月26日 93

-

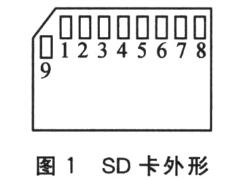

SD卡TF卡引脚定义2024年11月26日 72

-

C语言string.h常用函数重点说明2024年11月22日 49

-

C语言下划线命名法2024年11月22日 57

-

C数组 结构体 联合体快速初始化2024年11月22日 48

热门文章

-

C99语法规则2024年11月16日 759

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 455

-

ARM9远程图像无线监控系统2012年07月03日 425

-

用单片机模拟2272软件解码2012年09月06日 303

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300