verilog设计经验

2012-06-02

12

一、组合逻辑 1、敏感变量的描述完备性 Verilog中,用always块设计组合逻辑电路时,在赋值表达式右端参与赋值的所有信号都必须在 always @(敏感电平列表)中列出,always中if语句的判断表达式必须在敏感电平列表中列出。如果在赋值表达式右端引用了敏感电平列表中没有列出的信号,在综合时将会为没有列出的信号隐含地产生一个透 ..

[查看全文]

verilog的键盘源码keypad—有去抖功能

2012-06-02

13

下面是转的一个源码,俺没有细看,有兴趣的看看,讲讲如何 // author: Dandy Nee // mail:dandynee@yeah.net // module: HW KeyScan Module // version:0.1 // ************************** // all functions are provided as if okay // run at your own risk // ************************** // // problem:there is one keyva ..

[查看全文]

基于VHDL语言的 IP 核验证

2012-06-02

16

摘要:探讨了IP核的验证与测试的方法及其和VHDL语言在IC设计中的应用.并给出了其在RISC8框架CPU核中的下载实例 引言 在IC(integrated circuit.集成电路)发展到超大规模阶段的今天,基于IP(Intellectual Property,知识产权)核的IC设计及其再利用是保证SoC(system onchip,片上系统)开发效率和质量的重要手段。如果能对IP ..

[查看全文]

TEXTIO及其在VHDL仿真中的应用

2012-06-02

于红旗

17

TEXTIO 在VHDL 仿真与磁盘文件之间架起了桥梁,使用文本文件扩展VHDL 的仿真功能。本文介绍TEXTIO 程序包,以一个加法器实例说明TEXTIO 的使用方法,最后使用ModelSim 对设计进行仿真,并分析仿真结果。 在对VHDL 源程序进行仿真时, 由于有的输入输出关系仅仅靠输入波形或编写testbench 中的信号输入是难以验证结果正确 ..

[查看全文]

fir滤波器的Verilog程序

2012-06-02

38

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date:17:01:38 10/09/06 // Design Name: // Module Name:ppeifir // Project Name: // Target Device: // Tool versions: // Description:用Verilog编写的fir滤波器程 ..

[查看全文]

浅谈VHDL/Verilog的可综合性以及对初学者的一些建议

2012-06-02

16

一、HDL不是硬件设计语言 过去笔者曾碰到过不少VHDL或Verilog HDL的初学者问一些相似的问题,诸如如何实现除法、开根号,如何写循环语句等等。在这个论坛上,也时常能看到一些网友提出这一类的问题。 对于这些问题,首先要明确的是VHDL和Veriglog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。HDL是Har ..

[查看全文]

可综合的Verilog FIFO存储器

2012-06-02

14

可综合的Verilog FIFO存储器 This example describes a synthesizable implementation of a FIFO. The FIFO depth and FIFO width in bits can be modified by simply changing the value of two parameters, `FWIDTH and `FDEPTH. For this example, the FIFO depth is 4 and the FIFO width is 32 bits. The input/output p ..

[查看全文]

Verilog代码编写规范

2012-06-02

17

一. 强调Verilog代码编写风格的必要性。 强调Verilog代码编写规范,经常是一个不太受欢迎的话题,但却是非常有必要的。 每个代码编写者都有自己的编写习惯,而且都喜欢按照自己的习惯去编写代码。与自己编写风格相近的代码,阅读起来容易接受和理解。相反和自己编写风格差别较大的代码,阅读和接受起来就困难一些。 曾有编程大师 ..

[查看全文]

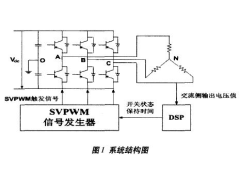

SVPWM信号发生器的VHDL实现

2012-06-02

吴晨光

12

近年来,DSP在SVPWM(空间矢量脉宽调制)控制领域得到了广泛应用。但是使用DSP单核心的控制方法仍然存在一些缺陷:基于软件的:DSP在实现SVPWM触发信号时需要较长的时钟周期;微处理器中不确定的中断响应会导致PWM脉冲的相位抖动。针对以上问题,本文提出了一种利用FPGA实现的SVPWM信号发生器,系统结构如图1所示 ..

[查看全文]

基于VHDL的异步串行通信电路设计

2012-06-02

李刚强

21

1 引 言 随着电子技术的发展,现场可编程门阵列 FPGA和复杂可编程逻辑器件CPLD的出现,使得电子系统的设计者利用与器件相应的电子CAD软件,在实验室里就可以设计自己的专用集成电路ASIC器件。这种可编程ASIC不仅使设计的产品达到小型化、集成化和高可靠性,而且器件具有用户可编程特性,大大缩短了设计周期,减少了设计费 ..

[查看全文]

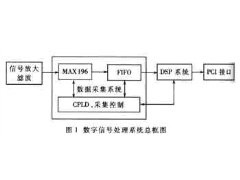

用Verilog HDL设计自动数据采集系统

2012-06-02

13

随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。从电子CAD、电子CAE到电子设计自动化(EDA ..

[查看全文]

针对C语言编程者的Verilog开发指南

2012-06-02

18

本文举例说明了如何用软件实现脉宽调制(PWM),如何将该设计转换成一个可以在FPGA中运行的逻辑块,并能利用存储器映射I/O接口通过软件完成对该逻辑块的控制。通过理解本文讨论的概念和内容,没有太多硬件知识的软件开发人员也能掌握在FPGA上开发硬件的技能。 在不远的将来,嵌入式系统设计师将能够根据哪个更有利于解决设 ..

[查看全文]

推荐文章

最新文章

热门文章