Verilog中模组(module)的概念

2012-06-02

10

模组(module)的概念 -------------------------------------------------------------------------------- Verilog中的基本单元是模组(module)。 模组代表一些可以用硬体实践的逻辑实体。 例如,一个模组可以是一个逻辑闸、一个三十二位元计数器、一个记忆体子系统、一个机算机系统或是一个用网路相连的多部电脑。 模 ..

[查看全文]

分频器的VHDL描述

2012-06-02

10

在数字电路中,常需要对较高频率的时钟进行分频操作,得到较低频率的时钟信号。我们知道,在硬件电路设计中时钟信号时非常重要的。 下面我们介绍分频器的VHDL描述,在源代码中完成对时钟信号CLK的2分频,4分频,8分频,16分频。 LIBRARYIEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IE ..

[查看全文]

SystemVerilog语言简介

2012-06-02

44

SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、 接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。SystemVerilog由Accellera开发,它主要定位在芯片的 ..

[查看全文]

Verilog阻塞式赋值与非阻塞式赋值的分析

2012-06-02

nsun

24

在Verilog HDL中,有两种过程性赋值方式,即阻塞式(blocking)和非阻塞式(non-blocking)。这两种赋值方式看似差不多,其实在某些情况下却有着根本的区别,如果使用不当,综合出来的结果和你所想得到的结果会相去甚远。 Tip:所谓过程性赋值就是指在initial或always语句内的赋值,它只能对寄存器数 据类型的变量赋值。 阻塞式 ..

[查看全文]

Verilog交通灯控制器程序

2012-06-02

6

交通灯控制器 /* 信号定义与说明: CLK: 为同步时钟; EN: 使能信号,为1 的话,则控制器开始工作; LAMPA: 控制A 方向四盏灯的亮灭;其中,LAMPA0~LAMPA3,分别控制A 方向的 左拐灯、绿灯、黄灯和红灯; LAMPB: 控制B 方向四盏灯的亮灭;其中,LAMPB0 ~ LAMPB3,分别控制B 方向的 左拐灯、绿灯、黄灯和红灯; ACOU ..

[查看全文]

Verilog Pli的基本使用方法(modelsim)

2012-06-02

19

内容未做证实,仅供参考。 1.hello.c文件内容 #include #include "veriuser.h" static PLI_INT32 hello() { printf("Hi there\n"); return 0; } s_tfcell veriusertfs[] = { {usertask, 0, 0, 0, hello, 0, "$hello"}, {0} /* last entry must be 0 */ }; 2.hello.v文件内容 module hello; initial begin $hello ..

[查看全文]

Verilog脉冲发生器程序

2012-06-02

万雪松

26

/*************************************************************************************** 实现功能简述 本模块主要功能是产生一个确定时钟周期长度(最长为256个时钟周期)的脉冲信号,可以自己设定脉冲长度,输出的脉冲信号与时钟上升沿同步 脉冲宽度 = pulsewide + 1 时钟周期; 输入一个启动信号后,可以产生一个 ..

[查看全文]

VHDL设计举例:步进电机控制器

2012-06-02

26

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.ALL; USE IEEE.std_logic_arith.ALL; ENTITY step_motor IS PORT( f, p, d: INSTD_LOGIC:='0'; speed : inSTD_LOGIC_VECTOR(1 downto 0); coil : OUTSTD_LOGIC_VECTOR(3 downto 0) ); END step_motor; ARCHITECTURE behavior OF s ..

[查看全文]

锁存器 vhdl源程序

2012-06-02

10

锁存器 vhdl Library IEEE ; use IEEE.std_logic_1164.all ; ENTITY latchinf IS PORT ( enable, data : IN BIT; q : OUT BIT ); END latchinf; ARCHITECTURE maxpld OF latchinf IS BEGIN latch : PROCESS (enable, data) BEGIN IF (enable = '1') THEN q END IF; END PROCESS latch; END maxpld;

[查看全文]

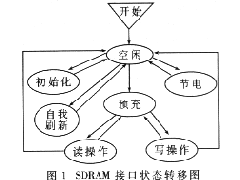

SDRAM接口的VHDL设计

2012-06-02

沙燕萍 曾烈光

22

SDRAM接口的VHDL设计 RAM(随机存取存储器?犑且恢衷诘缱酉低持杏τ霉惴旱钠骷?,通常用于数据和程序的缓存。随着半导体工业的发展,RAM获得了飞速的发展,从RAM、DRAM(Dynamic RAM,即动态RAM)发展到SDRAM(Synchronous Dynamic RAM,即同步动态RAM),RAM的容量越来越大、速度越来越高,可以说存储器的容 ..

[查看全文]

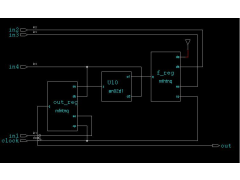

一个简单的总线轮询仲裁器Verilog代码

2012-06-02

18

下面这个是以输入信号作为状态机的转移条件,写得比较冗余: // // Verilog Module demo1_lib.bus_arbitor.arch_name // // Created: //by - Newhand //in - Shanghai ZhangJiang //at - 20:39:41 2003-12-03 // using Mentor Graphics HDL Designer(TM) // ///////////////////////////////////////////////////////// ..

[查看全文]

提高NC-Verilog仿真效率的技巧

2012-06-02

17

本文回顾了一些NC-Verilog的命令行选项,并说明这些选项如何影响仿真效率。同时,我们也展示了一些技巧,以帮助用户的NC-Verilog在最大效率下仿真一个设计和测试平台。 文中的命令行选项语法采用单步启动的方式(ncverilog +),这些选项也适合多步启动模式(ncvlog, ncelab, 或ncsim)。 安装最新发布的软件 首先确认你是否安 ..

[查看全文]

推荐文章

最新文章

热门文章