FPGA的FIR抽取滤波器的设计

2012-06-02

佟力永

11

1、引言 抽取滤波器广泛应用在数字接收领域,是数字下变频器的核心部分。目前,抽取滤波器的实现方法有3种:单片通用数字滤波器集成电路、DSP和可编程逻辑器件。使用单片通用数字滤波器很方便,但字长和阶数的规格较少,不能完全满足实际需要。使用DSP虽然简单,但程序要顺序执行,执行速度必然慢。现场可编程门阵列(FPGA ..

[查看全文]

基于FPGA的FIR滤波器的实现

2012-06-02

郭继昌 向 晖 滕建辅 李香萍

23

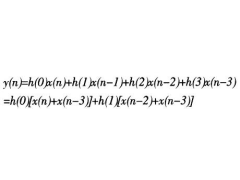

摘 要: 提出了一种采用现场可编程门阵列器件 FPGA并利用窗函数法实现线性 FIR数字滤波器硬件电路的方案,并以一个十六阶低通 FIR数字滤波器电路的实现为例说明了利用Xilinx公司 XC4000系列芯片的设计过程。设计的电路通过软件程序进行了验证和硬件仿真,结果表明电路工作正确可靠,能满足设计要求。 关键词: FPGA FIR数字滤 ..

[查看全文]

FPGA直接数字频率合成器的设计

2012-06-02

周俊峰 陈 涛

9

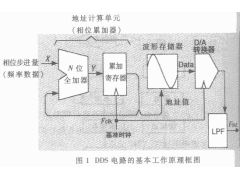

摘要:介绍了利用Altera的FPGA器件(ACEX EP1K50)实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。 关键词:直接数字频率合成(DDS) 现场可编程门阵列(FPGA) 直接数字频率合成(Direct Digital Fraquency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需要波形的一种新的频率 ..

[查看全文]

FPGA与DS18B20型温度传感器通信的实现

2012-06-02

李农

16

摘要:介绍利用ACTEL公司的APA150型现场可编程门阵列(FPGA)实现对DS18B20型温度传感器的通信控制,使CPU可以方便地从FPGA中读取温度测量结果和DS18B20的48位ID值。 1 引言 DS18B20是DALLAS公司生产的一线式数字温度传感器,采用3引脚TO-92型小体积封装;温度测量范围为-55℃~+125℃,可编程为9位~12位A/D转 ..

[查看全文]

Xilinx FPGA开发环境的配置

2012-06-02

风子心

24

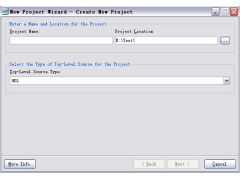

一、配置Modelsim ISE的Xilinx的仿真库 1、编译仿真库: A、先将Modelsim安装目录C=Modeltech_6.2b下面的modelsim.ini改成存档格式(取消只读模式); B、在DOS环境中,进入Xilinx的根目录,然后依次进入bin,nt目录; C、运行compxlib -s mti_se -f all -l all -o C:Modeltech_6.2bxilinx_libs。 注意:需要根据你安装的modelsim目录 ..

[查看全文]

用FPGA实现非标码速向标准码速的调整

2012-06-02

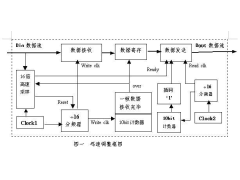

33

摘要:本文主要讨论了如何利用FPGA可编程芯片实现计算机输出的异步非标码速(如9.6k、19.2k、57.6k、115.2k、460.8k等)到其邻近的标准码速(如64k、128k、256k、512k)的调整,实现该数据与通用传输系统的适配,以便能进行远程监控。 关键词:码速调整 FPGA 一、概述 现在,利用计算机进行异地数据采集正应用到越来越 ..

[查看全文]

基于单片机P89C61X2的FPGA配置

2012-06-02

胡远望

10

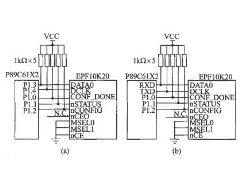

大部分FPGA采用基于SRAM(静态随机存储器)的查找表逻辑形成结构,就是用SRAM构成逻辑函数发生器。SRAM工艺的芯片在掉电后信息就会丢失,需要外加一片专用配置芯片。在上电时,由这个专用配置芯片把数据加载到FPGA中,然后FPGA就可以正常工作。这就是在线可重配置ICR(In-Circuit Reconfigurability)方式。 Altera公 司生 ..

[查看全文]

如何搭建Xilinx FPGA开发环境

2012-06-02

风子心

6

一、计算机硬件环境要求 : 1、操作系统: Microsoft Windows XP Home Edition SP2 2、基本配置: A、处理器:Intel CPU T2050 1.6GHz B、内存:512MB C、硬盘:60GB(其中软件安装的空问需要3GB) 补充: 上面的配置为笔记本的配置。因此对显卡没有什么特殊的要求。有条件的话,尽可能选择更高的配置。这样软件跑起来会更快。 ..

[查看全文]

基于 Modelsim FLI 接口的FPGA仿真技术

2012-06-02

胡军强 李津生 洪佩琳

10

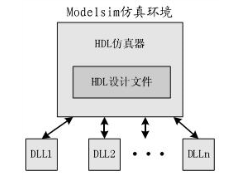

摘要:本文介绍了如何利用modelsim提供的FLI(Foreign Language Interface)接口进行VHDL设计文件的协同仿真,给出了协同仿真的意义以及协同仿真的程序结构和系统结构。 关键词:FPGA,仿真软件,协同仿真 1、Modelsim 及 FLI接口介绍 Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述语言仿真 ..

[查看全文]

Altera FPGA、CPLD 学习笔记

2012-06-02

11

1.硬件设计基本原则 速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用 & ..

[查看全文]

IIR数字滤波器的FPGA实现

2012-06-02

魏国华

10

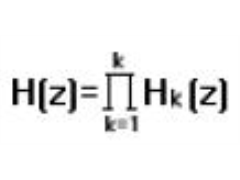

摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此设计扩展性好,便于调节滤波器的性能,可以根据不同的要求在不同规模的FPGA上加以实现。 IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同 ..

[查看全文]

基于FPGA 的高阶全数字锁相环的设计与实现

2012-06-02

单长虹 王彦 陈文光 陈忠泽

7

摘要:提出了一种实现高阶全数字锁相环的新方法。该锁相环以数字比例积分控制取代了传统的一些数字环路滤波控制方法,具有电路结构简单、控制灵活、跟踪精度高、环路性能好和易于集成的特点。文中介绍了该高阶全数字锁相环的系统结构和工作原理,对其性能进行了理论分析和计算机仿真。应用EDA 技术设计了该系统,并用FPGA实 ..

[查看全文]

推荐文章

最新文章

热门文章