Verilog HDL设计练习进阶(九)

2012-06-02

10

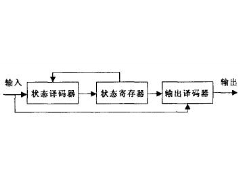

练习九.利用状态机的嵌套实现层次结构化设计 目的:1.运用主状态机与子状态机产生层次化的逻辑设计; 2.在结构化设计中灵活使用任务(task)结构。 在上一节,我们学习了如何使用状态机的实例。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是状态机套用状态机,从而形成树状的控制核心。这一点 ..

[查看全文]

VHDL的CRC编码器的设计

2012-06-02

郑春来

39

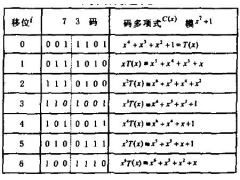

CRC码是线性分组码的一个重要子集,它是为了保证通信系统中的数据传输可靠性而采取的信道编码技术。CRC码除了具有分组码的线性外,还具有循环性,其码字结构一般用符号(n,k)表示,其中,n是该码组中的码元数,k是信息码位数,r=n-k是监督码元位数。循环码具有许多特殊的代数性质,这些性质有助于按照要求的纠错能力系统地 ..

[查看全文]

VHDL设计的消抖与滤波

2012-06-02

18

在同一块电路板上,由于信号线的走线过长而产生的高频毛刺我们可以通过在接近输入端串联一个100欧左右的电阻来滤除。但是对于板外信号,或者板内其他干扰造成较大的抖动时只好采用积分电路来滤波,即串一个电阻还要并一个电容接地。 同样在VHDL中我们可以采用类似的办法,对于小于触发器建立时间的毛刺可以用时钟打一下实现 ..

[查看全文]

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)

2012-06-02

常晓明 李媛媛

37

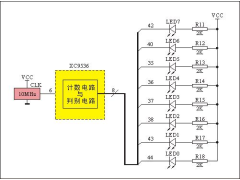

Verilog-HDL与CPLD/FPGA设计应用讲座 第 8 讲 用Verilog-HDL做CPLD设计 时序逻辑电路的实现 8.1 闪烁灯的实现 8.2 流水灯的实现 8.3 可编程单脉冲发生器 在第七讲中,已经介绍了组合逻辑电路的实现。组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。时序逻辑电路则不同于它,其特点是:在任意 ..

[查看全文]

VHDL设计中的电路简化问题

2012-06-02

14

摘 要 :从描述方法、设计规则、逻辑函数分析了VHDL设计中容易引起电路复杂化的原因,并提出了相应的解决方法。 近年来,随着集成电路技术的发展,用传统的方法进行芯片或系统设计已不能满足要求,迫切需要提高设计效率。在这样的技术背景下,能大大降低设计难度的VHDL设计方法正越来越广泛地被采用。但是VHDL设计是行为级 ..

[查看全文]

Verilog HDL代码描述对状态机综合的研究

2012-06-02

李玲 王祖强 陈东海

10

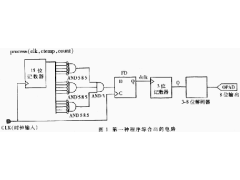

1 引言 Verilog HDL作为当今国际主流的HDL语言,在芯片的前端设计中有着广泛的应用。它的语法丰富,成功地应用于设计的各个阶段:建模、仿真、验证和综合等。可综合是指综合工具能将Verilog HDL代码转换成标准的门级结构网表,因此代码的描述必须符合一定的规则。大部分数字系统都可以分为控制单元和数据单元两个部分,控制单元 ..

[查看全文]

分频器的VHDL描述

2012-06-02

10

在数字电路中,常需要对较高频率的时钟进行分频操作,得到较低频率的时钟信号。我们知道,在硬件电路设计中时钟信号时非常重要的。 下面我们介绍分频器的VHDL描述,在源代码中完成对时钟信号CLK的2分频,4分频,8分频,16分频。 LIBRARYIEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IE ..

[查看全文]

Verilog HDL设计练习进阶(二)

2012-06-02

12

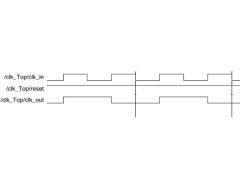

练习二. 简单时序逻辑电路的设计 目的:掌握基本时序逻辑电路的实现。 在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型,我们通常使用always块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个1/2分频器的可综合模型。 // half_clk.v: module half_clk( ..

[查看全文]

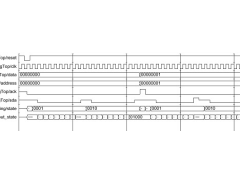

我的仿真工作流程(Verilog/Modelsim+Debussy)

2012-06-02

31

这是献给大家的第二篇,文章详细说明了本人近一年来,自己摸索出来的一套仿真工作流程。接触过Modelsim这类软件的朋友可能都会感觉上手比较困难,原因有二:一、对仿真机制不了解,对基于source+testbench的工作流程不熟悉(大多数朋友接触FPGA仿真可能以waveform的方式);二、对软件的安装和使用不熟悉,Modelsim软 ..

[查看全文]

Verilog交通灯控制器程序

2012-06-02

6

交通灯控制器 /* 信号定义与说明: CLK: 为同步时钟; EN: 使能信号,为1 的话,则控制器开始工作; LAMPA: 控制A 方向四盏灯的亮灭;其中,LAMPA0~LAMPA3,分别控制A 方向的 左拐灯、绿灯、黄灯和红灯; LAMPB: 控制B 方向四盏灯的亮灭;其中,LAMPB0 ~ LAMPB3,分别控制B 方向的 左拐灯、绿灯、黄灯和红灯; ACOU ..

[查看全文]

用VHDL设计乐曲发生器

2012-06-02

姜田华

69

1 概述随着EDA 技术的进展,基于可编程 ASIC 的数字电子系统设计的完整方案越来越受到人们的重视,并且以 EDA 技术为核心的能在可编程 ASIC 上进行系统芯片集成的新设计方法,也正在快速地取代基于 PCB板的传统设计方式。 与利用微处理器(CPU 或MCU)来实现乐曲演奏相比,以纯硬件完成乐曲演奏电路的逻辑要复杂得多,如果不 ..

[查看全文]

Verilog-HDL仿真软件ModelSim的基本操作

2012-06-02

常晓明

15

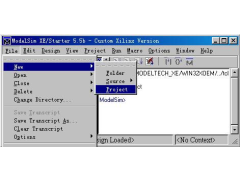

Verilog-HDL与CPLD/FPGA设计应用讲座 第 4 讲 Verilog-HDL仿真软件的基本操作 4.1 建立新的工程文件 4.2 一个最简单的仿真实例 在本讲以Xilinx WebPACK 4.1 ModelSim XE Starter为例,说明仿真软件的基本操作。 4.1 建立新的工程文件 启动Xilinx WebPACK 4.1 ModelSim XE Starter后,选中【File】菜单中的【New】菜单项, ..

[查看全文]

推荐文章

最新文章

热门文章