S3C2410 bootloader(vivi)阅读笔记

2012-06-02

15

建议读一读《嵌入式系统Boot Loader技术内幕》(詹荣开著)。什么是Bootloader就不再这里废话了,看看上面的文章就明了了。 Bootloader有很多种,如本文将要阅读的vivi,除此之外还有uboot,redboot,lilo等等。Vivi 是韩国mizi公司专门为三星s3c2410芯片设计的Bootloader。 先来看看vivi的源码树: vivi-+-arch-+-s3c2410 |-D ..

[查看全文]

51单片机控制DDS芯片AD9851的源程序

2012-06-02

20

;==================定义单片机与DDS芯片的连接======== DDS_DATA BIT P0.0 DDS_WCLK BIT P0.1 DDS_FQUD BIT P0.2 ;=================================================== ;==================定义DDS控制数据的存放地址======== DDS_DATA0 DATA 40H DDS_DATA1 D ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第9章 仿真的故障排...

2012-06-02

58

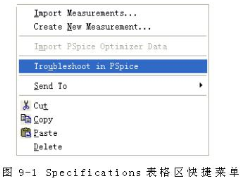

第9章 仿真的故障排除 在运行高级分析工具的过程中,由于操作失误、参数设置不合理等方面的原因,常常出现错误信息或者系统仿真不能运行等情况,用户往往得不到理想的分析结果,面对这些存在的难题,不能坐着发闷,要积极的解决问题。本章主要介绍运用故障排除分析工具解决存在问题的使用方法及高级分析中一般性故障的解决方 ..

[查看全文]

uCOS II就绪表(Ready List)分析

2012-06-02

21

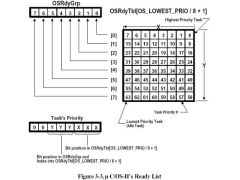

3.0 就绪表(Ready List) 每个任务被赋予不同的优先级等级,从0级到最低优先级OS_LOWEST_PR1O,包括0和OS_LOWEST_PR1O在内(见文件OS_CFG.H)。当uCOS II初始化的时候,最低优先级OS_LOWEST_PR1O总是被赋给空闲任务idle task。注意,最多任务数目OS_MAX_TASKS和最低优先级数是没有关系的。用户应用程序可以 ..

[查看全文]

Protel原理图/PCB到Cadence的数据转换

2012-06-02

19

随着PCB设计的复杂程度和高速PCB设计需求的不断增加,越来越多的PCB设计者、设计团队选择Cadence 的设计平台和工具。但是,由于没有Protel数据到Cadence数据直接转换工具,长期以来如何将现有的基于Protel平台的设计数据转化到 Cadence平台上来一直是处于平台转化期的设计者所面临的难题。 在长期实际的基础上,结合现有 ..

[查看全文]

PADS2005 SP2使用手记

2012-06-02

22

(主要是针对POWERLOGIC) 由于本人最近要用POWERLOGIC画原理图,发现PADS2005中的POWERLOGIC存在不少的问题! 二、 两个版本都延续了线终端的功能这个方面已经和ORCAD相同,这样可以简化图纸,不用一一去相连起来,只要在一张图相同的网络就可自动的连接,大大的减少了工作量! 三、 下面的就是最大的缺点(个人认 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第二章 OrCAD 10.3...

2012-06-02

20

OrCAD10.3是OrCAD a Cadence product family 公司于2004年11月推出的电子设计自动化(EDA)软件系统。其中包括三个主要部分: 锁定元件信息系统的原理图输入器(Capture CIS); 模拟和混合信号仿真(PSpice A/D)和其高级分析(PSpice –AA); 印刷电路板设计(Layout Plus)形成Gerber文件可与Protel等PCB软 ..

[查看全文]

16位ADC提供19位分辨率的电路设计

2012-06-02

21

许多数据采集系统都要求高精度和快速采集数据,以便允许该系统能够检测小信号并且能将更多的传感器通道聚集在同一系统。传感器通道越多,系统的外形就能够越小,成本和功耗也越低。远程光通信和医用设备(例如,CT扫描仪)即得益于快速和高精度的数据采集系统。在光功率系统(例如,激光泵)中,需要不断监视其功率水平。在 ..

[查看全文]

推荐文章

最新文章

热门文章