摘要:简要叙述了常用的信号处理系统的类型与处理机结构,介绍了正逐步得到广泛应用的DSP+FPGA处理机结构,在此基础上提出了一种实时信号处理的线性流水阵列,并举例说明了该结构的具体实现,最后分析说明了此结构的优越性。

实时信号处理系统要求必须具有处理大数据量的能力,以保证系统的实时性;其次对系统的体积、功耗、稳定性等也有较严格的要求。实时信号处理算法中经常用到对图象的求和、求差运算,二维梯度运算,图象分割及区域特征提取等不同层次、不同种类的处理。其中有的运算本身结构比较简单,但是数据量大,计算速度要求高;有些处理对速度并没有特殊的要求,但计算方式和控制结构比较复杂,难以用纯硬件实现。因此,实时信号处理系统是对运算速度要求高、运算种类多的综合性信息处理系统。

1 信号处理系统的类型与常用处理机结构

根据信号处理系统在构成、处理能力以及计算问题到硬件结构映射方法的不同,将现代信号处理系统分为三大类:

- 指令集结构(ISA)系统。在由各种微处理器、DSP处理器或专用指令集处理器等组成的信号处理系统中,都需要通过系统中的处理器所提供的指令系统(或微代码)来描述各种算法,并在指令部件的控制下完成对各种可计算问题的求解。

- 硬连线结构系统。主要是指由专用集成电路(ASIC)构成的系统,其基本特征是功能固定、通常用于完成特定的算法,这种系统适合于实现功能固定和数据结构明确的计算问题。不足之处主要在于:设计周期长、成本高,且没有可编程性,可扩展性差。

- 可重构系统。基本特征是系统中有一个或多个可重构器件(如FPGA),可重构处理器之间或可重构处理器与ISA结构处理器之间通过互连结构构成一个完整的计算系统。

从系统信号处理系统的构成方式来看,常用的处理机结构有下面几种:单指令流单数据流(SISD)、单指令流多数据流(SIMD)、多指令流多数据流(MIMD)。

- SISD结构通常由一个处理器和一个存贮器组成,它通过执行单一的指令流对单一的数据流进行操作,指令按顺序读取,数据在每一时刻也只能读取一个。弱点是单片处理器处理能力有限,同时,这种结构也没有发挥数据处理中的并行性潜力,所以在实时系统或高速系统中,很少采用SISD结构。

- SIMD结构系统由一个控制器、多个处理器、多个存贮模块和一个互连网络组成。所有“活动的”处理器在同一时刻执行同一条指令,但每个处理器执行这条指令时所用的数据是从它本身的存储模块中读取的。对操作种类多的算法,当要求存取全局数据或对于不同的数据要求做不同的处理时,它是无法独立胜任的。另外,SIMD 一般都要求有较多的处理单元和极高的I/O吞吐率,如果系统中没有足够多的适合SIMD处理的任务,采用SIMD是不合算的。

- MIMD结构就是通常所指的多处理机,典型的MIMD系统由多台处理机、多个存储模块和一个互连网络组成,每台处理机执行自己的指令,操作数也是各取各的。MIMD结构中每个处理器都可以单独编程,因而这种结构的可编程能力是最强的。但由于要用大量的硬件资源解决可编程问题,硬件利用率不高。

2 DSP+FPGA结构

随着大规模可编程器件的发展,采用DSP+ASIC结构的信号处理系统显示出了其优越性,正逐步得到重视。与通用集成电路相比,ASIC芯片具有体积小、重量轻、功耗低、可靠性高等几个方面的优势,而且在大批量应用时,可降低成本。

现场可编程门阵列(FPGA)是在专用ASIC的基础上发展出来的,它克服了专用ASIC不够灵活的缺点。与其他中小规模集成电路相比,其优点主要在于它有很强的灵活性,即其内部的具体逻辑功能可以根据需要配置,对电路的修改和维护很方便。目前,FPGA的容量已经跨过了百万门级,使得FPGA成为解决系统级设计的重要选择方案之一。

DSP+FPGA结构最大的特点是结构灵活,有较强的通用性,适于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统易于维护和扩展,适合于实时信号处理。

实时信号处理系统中,低层的信号预处理算法处理的数据量大,对处理速度的要求高,但运算结构相对比较简单,适于用FPGA进行硬件实现,这样能同时兼顾速度及灵活性。高层处理算法的特点是所处理的数据量较低层算法少,但算法的控制结构复杂,适于用运算速度高、寻址方式灵活、通信机制强大的DSP芯片来实现。

3 线性流水阵列结构

在我们的工作中,设计并实现了一种实时信号处理结构。它采用模块化设计和线性流水阵列结构(图1)。

这种线性流水阵列结构具有如下特点:

- 接口简单。各处理单元(PU)之间采用统一的外部接口。

- 易于扩充和维护。各个PU的内部结构完全相同,而且外部接口统一,所以系统很容易根据需要进行硬件的配置和扩充。当某个模块出现故障时,也易于更换。

- 处理模块的规范结构能够支持多种处理模式,可以适应不同的处理算法。

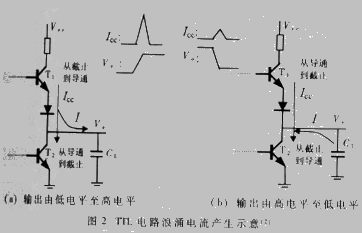

每个PU的核心由DSP芯片和可重构器件FPGA组成,另外还包括一些外围的辅助电路,如存储器、先进先出(FIFO)器件及FLASHROM等(图2)。可重构器件电路与DSP处理器相连,利用DSP处理器强大的I/O功能实现单元电路内部和各个单元之间的通信。从DSP的角度来看,可重构器件FPGA相当于它的宏功能协处理器(Co-processor)。

PU中的其他电路辅助核心电路进行工作。DSP和FPGA各自带有RAM,用于存放处理过程所需要的数据及中间结果。FLASHROM中存储了DSP的执行程序和FPGA的配置数据。先进先出(FIFO)器件则用于实现信号处理中常用到的一些操作,如延时线、顺序存储等。每个PU单独做成一块PCB,各级PU之间通过插座与底板相连。底板的结构很简单,主要由几个串连的插座构成,其作用是向各个PU提供通信通道和电源供应。可以根据需要安排底板上插座的个数,组成多级线性阵列结构。这种模块化设计的突出优点在于,它使得对系统的功能扩充和维护变得非常简单。需要时,只要插上或更换PU电路板,就可以实现系统的扩展和故障的排除。每一级PU中的DSP都有通信端口与前级和后级PU电路板相连,可以很方便地控制和协调它们之间的工作。

4 应用实例

我们应用上述线性流水阵列结构实现了一个实时目标检测系统,该系统的任务主要是接收摄像头输出的灰度图象,经预处理、编码、直线拟合和目标识别后,输出结果到PC机显示。在这个任务中,预处理模块包括抽样、卷积和编码等步骤,属于低层的处理,其运算数据量大,但运算结构较规则,适于用FPGA进行纯硬件实现;而直线拟合及目标识别等高层图象处理算法,所处理的数据量相对较少,但要用到多种数据结构,其控制也复杂得多,我们用DSP编程来实现。

重构处理模块采用的是Xilinx公司的XC5200系列FPGA芯片。这是一种基于SRAM的现场可编程门阵列。表1给出了XC5200 系列FPGA的一些参数。

表1 XC5200系列FPGA的一些参数

|

器件 |

XC5204 |

XC5206 |

XC5210 |

XC5215 |

|

逻辑单元 |

480 |

784 |

1296 |

1936 |

|

最大逻辑门 |

6000 |

10000 |

16000 |

23000 |

|

多功能块 |

10×12 |

14×14 |

18×18 |

22×22 |

|

CLB |

120 |

196 |

324 |

484 |

|

触发器 |

480 |

784 |

1296 |

1936 |

|

I/O |

124 |

148 |

196 |

244 |

XC5200系列FPGA逻辑功能的实现由内部规则排列的逻辑单元阵列(LCA)来完成,它是FPGA的主要部分。LCA的核心是可重构逻辑块(CLB),四周是一些输入/输出块(IOB)。CLB和IOB之间通过片内的布线资源相连接。LCA由配置代码驱动,CLB和IOB的具体逻辑功能及它们的互联关系由配置数据决定。整个FPGA模块的设计实现在Xilinx公司的Foundation 2.1i开发平台上完成。该系统支持设计输入、逻辑仿真、设计实现(设计综合)和时序仿真等系统开发全过程。

在选用DSP芯片时,主要应考虑性能能否满足快速判读算法的要求,具体说就是要求选择那些指令周期短、数据吞吐率高、通信能力强、指令集功能完备的处理器,同时也要兼顾功耗和开发支持环境等因素。表2列出了一些常用微处理器的性能参数。

我们选择的是应用广泛、性价比较高的TMS320C40芯片。它是美国TI公司推出的为满足并行处理需求的32位浮点DSP。主要特性如下:

表2 常用微处理器对照表

|

处理器类型 |

DSP(Motorola) |

ADSP |

TMS320 |

||||

|

96002 |

56156 |

21020 |

2101 |

C30 |

C40 |

C50 |

|

|

字长/bit |

32 |

16 |

32 |

16 |

32 |

32 |

16 |

|

指令周期/ns |

50 |

50 |

50 |

60 |

33 |

25 |

50 |

|

1024浮点FFT时间/ms |

1.04 |

2.33 |

0.96 |

2.07 |

2.36 |

1.93 |

3.42 |

- 外部时钟40MHz,内部时钟20MHz,所有指令均单周期完成,处理器内部采用高度并行机制,可同时进行多达11项各类操作。

- 两套相同的外部数据、地址总线,支持局部存储器和全局共享存储器。

- 6个高速并行通信口,采用异步传输方式,最大速率可达20Mb/s。通过令牌传递可灵活实现数据双向传输,这种结构很适合C40之间的互连。

- 6个DMA通道,每个通道的最大速率可达20Mb/s。DMA内部总线与CPU的地址、数据、指令总线完全分开,避开了总线使用上的瓶颈。

从结构和功能上看,C40很适合与可重构器件互相配合起来构成高速、高精度的实时信息处理系统,并完全可以胜任图像信息的实时处理任务;此外,C40的开发系统也比较完备,支持C语言和汇编语言编程,能够方便地进行算法移植和软/硬件的协同设计。

衡量系统的整体性能不仅要看所使用的器件和所能完成的功能,还要看器件之间采用怎样的互连结构。XC5200可以完成模块级的任务,起到DSP的协处理器的作用。它的可编程性使它既具有专用集成电路的速度,又具有很高的灵活性。C40内部结构的主要优势是:所有指令的执行时间都是单周期,指令采用流水线,内部的数据、地址、指令及DMA总线分开,有较多的寄存器。这些特征使它有较高的处理速度。FPGA具有硬件的高速性,而C40具有软件的灵活性,从器件上考察,能够满足处理复杂算法的要求。同时,C40的6个通信口和6个DMA通道使其能够在不被中断的情况下比较从容地应付与外界大量的数据交换。

从PU内部互连来看,C40使用了专用的通信口完成与FPGA的互连,能够保证在任何情况下FPGA与C40的数据通道的畅通。另外,FPGA和C40各自都有输入端口,使得系统的处理结构多样化。比如,FPGA可以作为处理流程中的一个模块,独立完成某项功能,也可以作为C40的协处理器,通过C40的调用来完成特定的子函数。底板将互连性延伸到PU之间,使得多个电路板能够组成多处理机系统。前级的C40既可以与下一级的C40通信,也可以将数据发送到下一级的FPGA。

综上所述,本文提出的基于DSP+FPGA的线性流水阵列结构,为设计中如何处理软硬件的关系提供了一个较好的解决方案。同时,该系统具有灵活的处理结构,对不同结构的算法都有较强的适应能力,尤其适合实时信号处理任务。

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 192

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261