练习七. 在Verilog HDL中使用任务(task)

目的:掌握任务在结构化Verilog HDL设计中的应用。

仅有函数并不能完全满足Veirlog HDL中的运算需求。当我们希望能够将一些信号进行运算并输出多个结果时,采用函数结构就显得非常不方便,而任务结构在这方面的优势则十分突出。任务本身并不返回计算值,但是它通过类似C语言中形参与实参的数据交换,非常快捷地实现运算结果的调用。此外,我们还常常利用任务来帮助我们实现结构化的模块设计,将批量的操作以任务的形式独立出来,这样设计的目的通常一眼看过去就很明了。

下面是一个利用task和电平敏感的always块设计比较后重组信号的组合逻辑的实例。可以看到,利用task非常方便地实现了数据之间的交换,如果要用函数实现相同的功能是非常复杂的;另外,task也避免了直接用一般语句来描述所引起的不易理解和综合时产生冗余逻辑等问题。

模块源代码:

//----------------- sort4.v ------------------

module sort4(ra,rb,rc,rd,a,b,c,d);

output[3:0] ra,rb,rc,rd;

input[3:0] a,b,c,d;

reg[3:0] ra,rb,rc,rd;

reg[3:0] va,vb,vc,vd;

always @ (a or b or c or d)

begin

{va,vb,vc,vd}={a,b,c,d};

sort2(va,vc);//va 与vc互换。

sort2(vb,vd);//vb 与vd互换。

sort2(va,vb);//va 与vb互换。

sort2(vc,vd);//vc 与vd互换。

sort2(vb,vc);//vb 与vc互换。

{ra,rb,rc,rd}={va,vb,vc,vd};

end

task sort2;

inout[3:0] x,y;

reg[3:0] tmp;

if(x>y)

begin

tmp=x;//x与y变量的内容互换,要求顺序执行,所以采用阻塞赋值方式。

x=y;

y=tmp;

end

endtask

endmodule

值得注意的是task中的变量定义与模块中的变量定义不尽相同,它们并不受输入输出类型的限制。如此例,x与y对于task sort2来说虽然是inout型,但实际上它们对应的是always块中变量,都是reg型变量。

测试模块源代码:

`timescale 1ns/100ps

`include "sort4.v"

module task_Top;

reg[3:0] a,b,c,d;

wire[3:0] ra,rb,rc,rd;

initial

begin

a=0;b=0;c=0;d=0;

repeat(5)

begin

#100a ={$random}%15;

b ={$random}%15;

c ={$random}%15;

d ={$random}%15;

end

#100 $stop;

sort4 sort4 (.a(a),.b(b),.c(c),.d(d), .ra(ra),.rb(rb),.rc(rc),.rd(rd));

endmodule

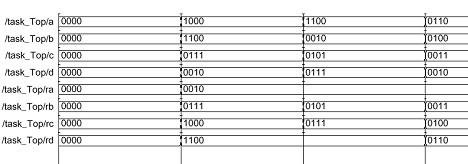

仿真波形(部分):

练习:设计一个模块,通过任务完成3个8位2进制输入数据的冒泡排序。要求:时钟触发任务的执行,每个时钟周期完成一次数据交换的操作。

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 192

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261