megafuction是一种可以在Quartus中使用的模块库。从MAX + PLUS开始就可以使用了。在Quartus中,该库增加了很多新模块,使得设计变得更加容易。

要使用megafuction,可以使用Tools菜单中的MegaWizard Plug-In Manager进行定制。该向导可以创建或者编辑设计文件来定义用户的meagfuction实例。也就是定制LPM功能。

下面举个altsyncram的例子。该megafunction是一种Quartus自带的模块。

该模块支持Cyclone、Cyclone II、HardCopy II、HardCopy Stratix、Stratix、Stratix II、Stratix GX系列芯片。这些芯片都是FPGA。

需要强调的一点是,在CPLD上做RAM是没有前途的。因为CPLD上没有专用的RAM,因此如果要用CPLD实现RAM,需要数量巨大的门电路,这样非常浪费芯片资源,而且RAM的尺寸做不大。

altsyncram的定义如下:

FUNCTION altsyncram (wren_a, wren_b, data_a[OPERATION_MODE != "ROM" ? WIDTH_A - 1 : 0..0],

data_b[(OPERATION_MODE == "BIDIR_DUAL_PORT") ? WIDTH_B - 1 : 0..0],

address_a[WIDTHAD_A - 1..0],

address_b[(OPERATION_MODE == "BIDIR_DUAL_PORT" # OPERATION_MODE == "DUAL_PORT") ?WIDTHAD_B - 1 : 0..0],

clock0, clock1, clocken0, clocken1, rden_b, aclr0, aclr1, addressstall_a,addressstall_b,

byteena_a[OPERATION_MODE != "ROM" ? ((WIDTH_A > 15) ? ((WIDTH_BYTEENA_A > 1 ?WDTH_BYTEENA_A-1 : 0)) : 0 ): 0..0],

byteena_b[OPERATION_MODE == "BIDIR_DUAL_PORT" ? ((WIDTH_B > 15)? (WIDTH_BYTEENA_B > 1? WIDTH_BYTEENA_B-1 : 0) : 0 ): 0..0] )

WITH (OPERATION_MODE, WIDTH_A, WIDTHAD_A, NUMWORDS_A, INDATA_ACLR_A, WRCONTROL_ACLR_A,

ADDRESS_ACLR_A, WIDTH_B, WIDTHAD_B, NUMWORDS_B, INDATA_REG_B, INDATA_ACLR_B,

WRCONTROL_WRADDRESS_REG_B, WRCONTROL_ACLR_B, ADDRESS_ACLR_B, OUTDATA_REG_A,

OUTDATA_ACLR_A, BYTEENA_ACLR_A, RDCONTROL_REG_B, RDCONTROL_ACLR_B, ADDRESS_REG_B,

OUTDATA_REG_B, OUTDATA_ACLR_B, BYTEENA_REG_B, BYTEENA_ACLR_B, INIT_FILE,

INIT_FILE_LAYOUT, MAXIMUM_DEPTH, WIDTH_BYTEENA_A, WIDTH_BYTEENA_B, BYTE_SIZE,

READ_DURING_WRITE_MODE_MIXED_PORTS, READ_DURING_WRITE_MODE_PORT_A,

READ_DURING_WRITE_MODE_PORT_B,

RAM_BLOCK_TYPE, CLOCK_ENABLE_INPUT_A, CLOCK_ENABLE_INPUT_B, CLOCK_ENABLE_OUTPUT_A,

CLOCK_ENABLE_OUTPUT_B, LOW_POWER_MODE, DEVICE_FAMILY )

RETURNS (q_a[WIDTH_A - 1..0],

q_b[(OPERATION_MODE == "DUAL_PORT" # OPERATION_MODE == "BIDIR_DUAL_PORT") ? WIDTH_B -1 : 0..0] );

这些参数的意思是:

wen_a:(可选)。输入写使能。当OPERATION_MODE参数被设置成ROM模式时,wren_a端口不可用。

wen_b:(可选)。输入写使能。当OPERATION_MODE参数被设置成BIDIR_DUAL_PORT时,wen_b端口可用

。

rden_b:(可选)。输入读使能输入端口。

data_a[](可选)。数据输入端口。数据宽度WIDTH_A-1..0。

data_b[](可选)。数据输入端口。数据宽度WIDTH_B-1..0。

address_a[](必要)。内存地址端口。地址宽度WIDTHAD_A-1..0。

address_b[](必要)。内存地址端口。地址宽度WIDTHAD_B-1..0。

clock0(必要)。存取时钟。

clock1(可选)。存取时钟。

clocken0(可选)。clock0的时钟使能。

clocken1(可选)。clock1的时钟使能。

aclr0(可选)。同步清除输入端1。

aclr1(可选)。同步清除输入端2。

byteteena_a[](可选)。字节使能输入端口。

byteteena_b[](可选)。字节使能输入端口。

addressstall_a(可选)。端口A的地址输入。

addressstall_b(可选)。端口B的地址输入。

输出端口

q_a[](必要)。数据输出端口0。输出端口WIDTH_A-1..0。该端口在OPERATION_MODE为SINGLE_PORT、BIDIR_DUAL_PORT或者ROM时有效。

q_b[](必要)。数据输出端口1。输出端口WIDTH_B-1..0。该端口在OPERATION_MODE为SINGLE_PORT、BIDIR_DUAL_PORT或者ROM时有效。

-

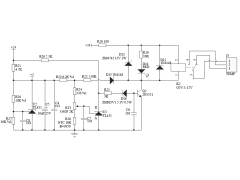

一款高温报警电路2024年11月13日 81

-

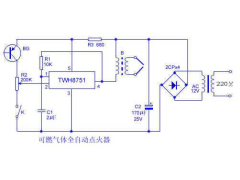

可燃气体全自动点火器2012年09月22日 76

-

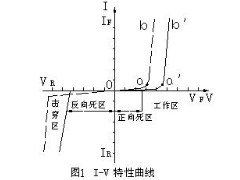

LED参数与特性2012年09月18日 118

-

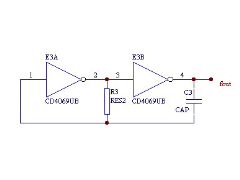

RC振荡电路的几种接法2012年09月10日 221

-

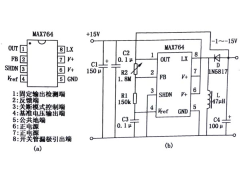

MAX764极性反转电路2012年08月24日 47

-

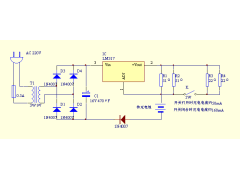

实用恒流充电器2012年08月18日 175

-

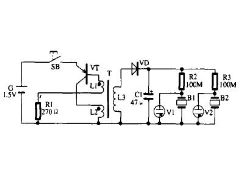

电子催眠器制作2012年08月15日 72

-

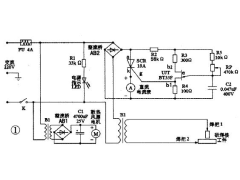

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4874

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499