FPGA内部有BLOCK RAM和分布式RAM,这些资源都可以作为ROM(ROM只是有初始值的RAM,而且该初始值不能改变)。有些低端的FPGA可能没有BLOCK RAM。本文主要介绍ROM的使用方法,RAM的使用方法类同。

打开XILINX的ISE,NEW SOURCE中选择IP,写好NAME,点击下一步。

在下图中选择你要的IP核。

第一个是使用分布式ROM-如果你的ROM不是很大的话,而且内部BLOCK RAM资源有限的情况下,使用分布式ROM可以为你节约不少BLOCK RAM,但是它会占用一些逻辑资源。

第二个是双口BLOCK RAM.

第三个是单口BLOCK RAM.

选择你想要使用的IP核,(以常用的单口BLOCK RAM为例)点击NEXT:

点击完成。

进入如下图界面。

在component name内填写模块名(要小写)

第二项选择READ ONLY(选READ AND WRITE 就是RAM),表示要生成只读的ROM。

Memory size 里填好ROM的宽度和深度,上图是一个256×16BIT的ROM。

点击NEXT进入下图。

这里默认就可以了。

再NEXT:

这里可以选择是CLK上升沿读数据还是下降沿读。

继续NEXT:

这里比较关键,要导入ROM的值。

在LOAD INIT FILE 项上打勾,点击LOAD FILE……出现下图,要你选择一个文件。

这个文件就是你要放在ROM中的数据,文件的后缀名是.COE。你可以自己建一个空的文本文件,然后把后缀名该为.COE即可。

文件内容的格式如下:

MEMORY_INITIALIZATION_RADIX=10;

MEMORY_INITIALIZATION_VECTOR=

32767,

32766,

32766,

32765,

32764,

32763,

32761,

32759,

32757,

……

32754;

注意:

第一行定义文件中的数据采用什么进制。可以使用10进制,2进制,16进制,数据大小不能超过你定义的数据宽度。

第二行照抄。

第三行开始就是数据了,每个数据用逗号","隔开,可以不分行,建议分行写,便于统计个数。

最后一个数据后用分号";"结束。

数据的个数必须和你定义的数据深度相同,否则会出错。

写好这个文件后,保存。

然后在点击LOAD FILE……,选择这个文件,点打开。

如果没有错误,可以点击旁边的show coefficients查看数据。如果数据很多(>512),建议不要使用此功能,可能会因数据太大而无法响应。

现在,可以点击GENERATE,产生代码了。

产生的代码中有个.MIF文件,就是ROM的数据的二进制文件。

其中的.V文件或.VHD就是生成的可综合的代码。

如上图的ROM_COS.XCO,选择它,双击VIEW HDL FUNCTIONAL MODEL

就可查看Verilog代码。

接下来,要删除ROM_COS.XCO,然后把ROM_COS.V添加进来。

接下来就可以综合了。

本文仅供参考学习,不得用于商业用途。

-

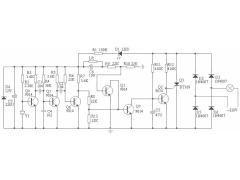

一款高温报警电路2024年11月13日 81

-

可燃气体全自动点火器2012年09月22日 76

-

LED参数与特性2012年09月18日 118

-

RC振荡电路的几种接法2012年09月10日 221

-

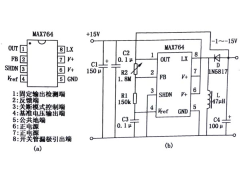

MAX764极性反转电路2012年08月24日 47

-

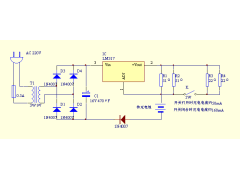

实用恒流充电器2012年08月18日 175

-

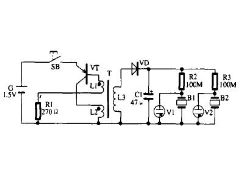

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4874

-

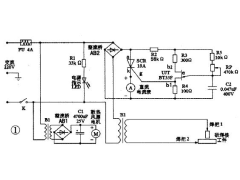

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

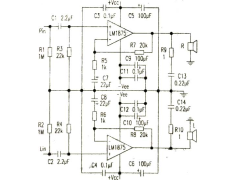

用LM1875替找TDA20302012年09月15日 777

-

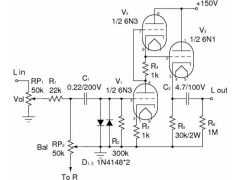

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

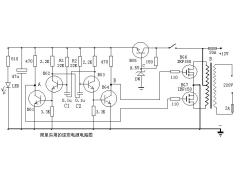

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499