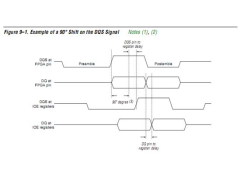

Cyclone II的DDR SDRAM接口实现

2013-01-14

24

在不增加电路板复杂度的情况下要想增强系统性能,改善数据位宽是一个有效的手段。通常来说,可以把系统频率扩大一倍或者把数据I/O管脚增加一倍来实现双倍的数据位宽。这两种方法都是我们不希望用到的,因为它们会增加整个设计系统的复杂度。在总的数据I/O管脚不变的情况下,使用双数据率(DDR)I/O管脚来传输和接收数据也能 ..

[查看全文]

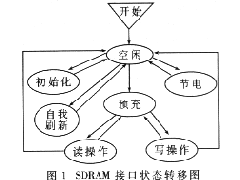

SDRAM控制器软核的Verilog设计

2012-11-23

18

目前,在很多通信芯片及系统的开发中,常常需要用到存储容量大、读写速度高的存储器。在各种随机存储器件中,SDRAM 的价格低、体积小、速度快、容量大,是比较理想的器件。但是,与SRAM相比较,SDRAM的控制逻辑复杂,使用很不方便。为了解决这个矛盾,需要设计专用的SDRAM控制器,使系统用户象使用SRAM一样方便的使 ..

[查看全文]

SDRAM接口的VHDL设计

2012-06-02

沙燕萍 曾烈光

18

SDRAM接口的VHDL设计 RAM(随机存取存储器?犑且恢衷诘缱酉低持杏τ霉惴旱钠骷?,通常用于数据和程序的缓存。随着半导体工业的发展,RAM获得了飞速的发展,从RAM、DRAM(Dynamic RAM,即动态RAM)发展到SDRAM(Synchronous Dynamic RAM,即同步动态RAM),RAM的容量越来越大、速度越来越高,可以说存储器的容 ..

[查看全文]

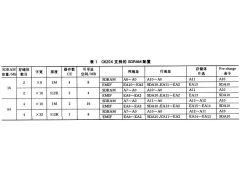

DSP片外高速海量SDRAM存储系统设计

2012-06-02

14

摘要:介绍使用同步动态RAM(SDRAM)扩展嵌入式DSP系统高速超大容量外部存储空间的设计方法;结合已成功实现的、基于TMS320C6201的数字信号处理系统,论述使用IS42S16400 SDRAM芯片设计DSP片外同步存储系统的具体实现方案;详细讨论TMS320c6201的EMI与SDRAM的接口设计及编程方法。在数字图像处理、航空航天等 ..

[查看全文]

SDRAM模块IP核调试经验

2012-06-02

rickyice

49

首先说明资源使用: 1.硬件: 基于HY57V561620CT-H的128M PC133内存条; ALTERA公司的EP1C6Q240C8芯片; 2.软件: lattice标准SDRAM模块; QUARTUS4.0; 下面说明我的艰辛的调试之路,呵呵。 我是从4月份开始学习verilog语言,然后从网上广泛搜集SDRAM模块,下载的有altera公司,有lattice的。经过对比,我选择了 ..

[查看全文]

推荐文章

最新文章

热门文章