Xilinx DCM的使用

2013-04-06

8

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构 ..

[查看全文]

FPGA DCM时钟管理单元的理解

2012-11-01

11

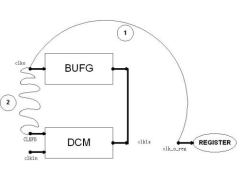

看Xilinx的Datasheet会注意到Xilinx的FPGA没有PLL,其实DCM就是时间管理单元。 ----------------------------------------------------- DCM概述 DCM内部是DLL(Delay Lock Loop(?)结构,对时钟偏移量的调节是通过长的延时线形成的。DCM的参数里有一个PHASESHIFT(相移),可以从0变到255。所以我们可以假设内部结 ..

[查看全文]

推荐文章

最新文章

热门文章