如何实现高速时钟信号的差分布线?

2013-03-23

11

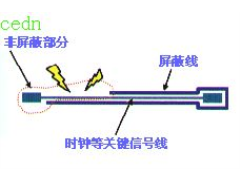

[提问] 在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线? [解答] 信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠 ..

[查看全文]

到底多高的频率才算高速信号?

2013-02-02

9

当信号的上升/下降沿时间 对于数字电路,关键是看信号的边沿陡峭程度,即信号的上升、下降时间,按照一本非常经典的书《High Speed Digtal Design>的理论,信号从10%上升到90%的时间小于6倍导线延时,就是高速信号! 即使8KHz的方波信号,只要边沿足够陡峭,一样是高速信号,在布线时需要使用传输线理论

[查看全文]

高频信号与高速信号的区别

2012-08-22

61

高速电路”已经成为当今电子工程师们经常提及的一个名词,但究竟什么是高速电路?这的确是一个“熟悉”而又“模糊”的概念。而事实上,业界对高速电路并没有一个统一的定义,通常对高速电路的界定有以下多种看法:有人认为,如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路已经占到了整个 ..

[查看全文]

推荐文章

最新文章

热门文章