静态时序分析(Static Timing Analysis)基础与应用(上)

2012-10-27

陳麒旭

31

前言 在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。此一趋势使得如何确保IC品质成为今日所有设计从业人员不得不面临之重大课题。静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC品质之课题,提供一个不错 ..

[查看全文]

静态时序分析在高速FPGA设计中的应用

2012-06-02

周海斌

27

摘要:介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进时序收敛的方法。结合设计实例,阐明了STA在高速、大规模FPGA开发中的应用。实践表明,随着数字设计复杂度的增加,在后端的时序验证环节,与传统的动 ..

[查看全文]

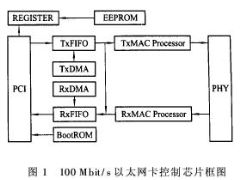

100Mbit/s以太网卡芯片设计与静态时序分析

2012-06-02

黎声华 莫迟

18

在专用集成电路的设计过程中,验证是最关键的一环,它贯穿了整个EDA设计流程.而在深亚微米芯片设计中,只有用实际的布图拓扑信息约束逻辑设计,才能得到准确的时序.在这种情形下静态时序分析应运而生,它可以利用从实际的布图拓扑信息得到的准确时序,根据设计规范的要求对设计进行检查而不需要测试向量,同时还能对设计本身作全面 ..

[查看全文]

静态时序分析(Static Timing Analysis)基础及应用(下)

2012-06-02

陈麒旭

23

前言 在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。此一趋势使得如何确保IC品质成為今日所有设计从业人员不得不面临之重大课题。静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者指定的时序下正常工作,对确保IC品质之课题,提供一个不错 ..

[查看全文]

推荐文章

最新文章

热门文章